## UNIVERSITY OF CALIFORNIA

#### Santa Barbara

# **Mixed Signal Neurocomputing Based on Floating-gate Memories**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Xinjie Guo

Committee in charge:

Professor Dmitri Strukov, Chair

Professor Kwang-Ting (Tim) Cheng

Professor Margaret Marek-Sadowska

Professor Li-C Wang

March 2017

# The dissertation of Xinjie Guo is approved.

| Kwang-Ting (Tim) Cheng         |

|--------------------------------|

|                                |

|                                |

|                                |

|                                |

| Margaret Marek-Sadowska        |

|                                |

|                                |

|                                |

| Li-C Wang                      |

| <u> </u>                       |

|                                |

|                                |

|                                |

| Dmitri Strukov Committee Chair |

March 2017

Mixed Signal Neurocomputing Based on Floating-gate Memories

Copyright © 2017

by

Xinjie Guo

#### **ACKNOWLEDGEMENTS**

I would like to gratefully acknowledge my advisor, Dr. Dmitri Strukov, for providing an opportunity of my stay at UCSB, supervising my research and reviewing this thesis. At the meantime, I want to show my deepest appreciation to Dr. Konstantin K. Likharev, Dr. Farnood Merrikh-Bayat, Dr. Mirko Prezioso, Mikhael Klachko and Dr. Ligang Gao for all the discussions we had and your help provided. Many thanks to all my other lab mates specially Dr. Gina Adam, Mohammad Bavandpour, Dr. Bhaswar Chakrabarti, Dr. Brian Hoskins, Dr. Advait Madhavan, M. Reza Mahmoodi and Dr. Elham Zamanidoost for the enjoyable working environment. I wish to thank my committee for the fruitful review of my thesis as well.

I also wish to thank those most important people in my life: my parents and my husband-Shaodi Wang. Without their endless love, support and paying out, I could never march this far and become who I am today.

## VITA OF XINJIE GUO March 2017

#### **EDUCATION**

Bachelor of Science in Microelectronics, Peking University, Berkeley, July 2011 Master of Science in Electrical Computer Engineering, University of California, Santa Barbara, June 2013

Doctor of Philosophy in Electrical Computer Engineering, University of California, Santa Barbara, March 2017 (expected)

#### PROFESSIONAL EMPLOYMENT

2011-2017: Researching Assistant, Department of Electrical Computer Engineering, University of California, Santa Barbara

#### **PUBLICATIONS**

- X. Guo, "Mixed Signal Neurocomputing Based on Floating-gate Memories", unpublished thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical Computer Engineering, University of California, Santa Barbara, 2017.

- F. Merrikh Bayat\*, X. Guo\*, M. Klachko, M. Prezioso, K.K. Likharev, and D.B. Strukov, "High-Performance Analog Neurocomputing with Nanoscale Floating-Gate Memory Cell Arrays", submitted to Science Advance. \*these authors have equal contribution.

- X. Guo, F. Merrikh Bayat, N. Do, M. Prezioso, K.K. Likharev, and D.B. Strukov, "Temperature-Insensitive Analog Vector-by-Matrix Multiplier Based on 55 nm NOR Flash Memory Cells", CICC'17, Austin, TX, May 2017.

- X. Guo\*, F. Merrikh-Bayat\*, L. Gao, B. D. Hoskins, F. Alibart, B. Linares-Barranco, L. Theogarajan, C. Teuscher, and D.B. Strukov, "Modeling and experimental demonstration of a Hopfield network analog-to-digital converter with hybrid CMOS/memristor circuits", Frontiers in Neuroscience, art. 488, Dec. 2015. \*these authors have equal contribution.

- F. Merrikh Bayat, X. Guo, and D. B. Strukov, "Exponential-weight multilayer perceptron", accepted to IJCNN'17, Anchorage, Alaska, May, 2017.

- F. Merrikh Bayat, X. Guo, M. Klachko, N. Do, K. Likharev, and D. Strukov, "Model-based high-precision tuning of NOR flash memory cells for analog computing applications", in: Proc. DRC'16, Newark, DE, June 2016, pp. 1-2.

- F. Merrikh Bayat, M. Prezioso, X. Guo, B. Hoskins, D.B. Strukov, and K.K. Likharev, "Memory technologies for neural networks", in: Proc. IMW'15, Monterey, CA, May 2015, pp. 1-4.

- F. Merrikh Bayat, X. Guo, H.A. Om'mani, N. Do, K.K. Likharev, and D.B. Strukov, "Redesigning commercial floating-gate memory for analog computing applications", in: Proc. ISCAS'15, Lisbon, Portugal, May 2015, pp. 1921-1924.

- L. Gao\*, F. Merrikh-Bayat\*, F. Alibart, X. Guo, B.D. Hoskins, K.-T. Cheng, and D.B. Strukov, "Digital-to-analog and analog-to-digital conversion with metal oxide memristors

for ultra-low power computing", in: Proc. NanoArch'13, New York, NY, July 2013 (best short paper award).

- Xinjie Guo, Shaodi Wang, Jin He, "A Novel Approach to Simulate Fin-width Line Edge Roughness Effect of FinFET Performance", IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC'10).

- Shaodi Wang, Xinjie Guo, Jin He, "Analytical subthreshold channel potential model of asymmetric gate under-lap gate-all-around MOSFET", IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC'10).

- Zhang Chenfei, Ma Chenyue, Guo Xinjie, "Forward Gated-Diode Method for Parameter Extraction of MOSFETs", Journal of Semiconductors.

#### **PATENTS**

- F. Merrikh Bayat, X. Guo, D.B. Strukov, H. Tran, N. Do, V. Tiwari, M, Reiten, "Deep Learning Neural Network Classifier Using Non-volatile Memory Array", U.S. application serial no. 62/337,760

- X. Guo, F. Merrikh Bayat, D.B. Strukov, H. Tran, N. Do, V. Tiwari, "Flash Memory Array with Individual Memory Cell Read, Program and Erase", U.S. application serial no. 62/337,751

#### **AWARDS**

- Dean's Scholarship, Peking University, 2010

- Industry Scholarship, Peking University, 2009

- 1st Prize in National Mathematics Olympiad in Province, 2006

#### **ABSTRACT**

# Mixed Signal Neurocomputing Based on Floating-gate Memories

by

## Xinjie Guo

Nervous systems inspired neurocomputing has shown its great advantage in object detection, speech recognition and a lot of other machine-learning technology-driven applications from speed and power efficiency. Among handful neurocomputing implementation approaches, analog nanoelectronic circuits are very appealing because they may far overcome digital circuits of the same functionality in circuit density, speed and energy efficiency. Device density is one of the most essential metrics for designing large-scale neural networks, allowing for high connectivity between neurons. Thanks to the high-density nature of traditional memory applications, building artificial neural networks with hybrid complementary metal oxide semiconductor (CMOS)/memory devices would enable the high parallelism as well as achieve the performance advantages.

Synapses, the most numerous elements of neural networks, are efficiently implemented by memory devices. This application, however, imposes a number of requirements, such as the continuous change of the memory resistance state, creating the need for novel engineering approaches. Here we report such engineering approaches for advanced commercial 180-nm ESF1 and 55-nm ESF3 NOR flash memory, facilitating fabrication and successful test of high performance analog vector-by-matrix multiplication which is the key operation performed at signal propagation through any neuromorphic network. Furthermore, we discuss the recent progress toward neuromorphic computing implementations based on nonvolatile floating-gate devices, in particular the experimental results for a prototype 28×28-binary-input, 10-output, 3-layer neuromorphic network based on arrays of highly optimized embedded nonvolatile floating-gate cells. The fabricated neuromorphic network's active components, including 101,780 floating-gate cells, have a total area below 1 mm<sup>2</sup>. The network has shown a 94.7% classification fidelity on the common MNIST benchmark, close to the 96.2% obtained in simulation. The classification of one pattern takes sub-1 µs time and sub-20 nJ energy – both numbers much better than for the best reported digital implementations of the same task. Estimates show that a straightforward optimization of the hardware, and its transfer to the already available 55-nm technology may increase this advantage to more than 100X in speed and 10000X in energy efficiency.

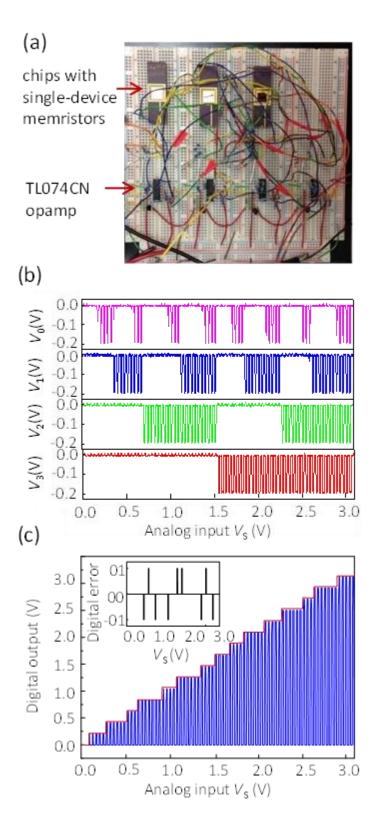

As pure analog circuits cannot address the noise accumulation problem, a practical solution would also require inclusion of analog-to-digital and digital-to-analog stages for signal restoration. High energy-efficient and compact data converters are therefore expected to play an important role in future computing platforms. We perform an experimental demonstration of 6-bit digital-to-analog (DAC) and 4-bit analog-to-digital conversion (ADC) operations implemented with a hybrid circuit consisting of Pt/TiO2-x /Pt resistive switching devices (also known as ReRAMs or memristors) and a CMOS operational amplifier (opamp). In particular, ADC is implemented with a Hopfield neural network circuit.

# TABLE OF CONTENTS

| ACKNOWLEGEMENTS                                                | iv  |

|----------------------------------------------------------------|-----|

| VITA                                                           | v   |

| ABSTRACT                                                       | vii |

| LIST OF TABLES                                                 | xi  |

| LIST OF FIGURES                                                | xii |

| I.Introduction                                                 | 1   |

| II. Memory Elements                                            | 5   |

| A. 180-nm ESF1 Floating-Gate                                   | 5   |

| 1. Device Characterization                                     | 6   |

| 2. Array Design                                                | 12  |

| B. 55-nm ESF3 Floating-Gate                                    | 17  |

| 1. Device Characterization                                     | 17  |

| 2. Array Design                                                | 22  |

| C. Memristive Device                                           | 25  |

| 1. Device Characterization                                     | 25  |

| 2. Modeling                                                    | 26  |

| III. High-Precision Tuning of Memory Elements                  | 28  |

| A. Model-Based Fast Tuning of 180-nm ESF1 Floating-Gate Array. | 28  |

| B. Tuning of 55-nm ESF3 Floating-Gate Array                    | 31  |

| IV. Vector by Matrix Multiplication                            | 35  |

| A. Based on 180-nm ESF1 Floating-Gate Array                    | 36  |

| B. Based on 55-nm ESF3 Floating-Gate Array                     | 40  |

| V. Mixed-Signal Neurocomputing Systems                             | 14 |

|--------------------------------------------------------------------|----|

| A. Fabricated Pattern Classifier based on NOR Flash Array4         | 44 |

| 1. Network Design                                                  | 44 |

| 2. Network Testing5                                                | 50 |

| 3. Network Evaluation                                              | 58 |

| B. Exponential-Weight Multilayer Perceptron with NOR Flash Array 5 | 59 |

| C. Hopfield Network with Hybrid CMOS/Memristor Circuits            | 54 |

| VI. Discussion                                                     | 81 |

| References                                                         | 34 |

| Appendix A List of Chips Fabricated9                               | 93 |

# LIST OF TABLES

| Table 1. Parameters for demonstrated Hopfield network ADC       | 80 |

|-----------------------------------------------------------------|----|

| Table 2. Speed and energy consumption of the convolutional part | 82 |

# LIST OF FIGURES

| Figure 1. SST's ESF-1 technology                                             | . 6 |

|------------------------------------------------------------------------------|-----|

| Figure 2. Readout characteristics of 180-nm ESF-1 memory cells               | . 7 |

| Figure 3. Analog tuning of 180-nm ESF-1 memory cells                         | . 9 |

| Figure 4. 180-nm ESF-1 memory cells' subthreshold conduction region          | 10  |

| Figure 5. 180-nm ESF-1 memory cells' retention and noise                     | 11  |

| Figure 6. 180-nm ESF-1 memory cells' recharging effects                      | 13  |

| Figure 7. High-precision tuning of cells of the modified 180-nm ESF-1 memory | 15  |

| Figure 8. SST's 55-nm ESF3 NOR flash memory cells                            | 17  |

| Figure 9. Modified 4-supercell ESF3 55-nm memory array                       | 18  |

| Figure 10. Drain-source current of a modified ESF3 cell                      | 19  |

| Figure 11. 55-nm ESF-3 memory cells' Retention measurements                  | 20  |

| Figure 12. 55-nm ESF-3 memory cells' temperature dependence                  | 21  |

| Figure 13. Vector-by-matrix multiplier based on ESF-3 memory cells           | 23  |

| Figure 14. Programming and erase inhibition of ESF-3 memory cells            | 24  |

| Figure 15. TEM images of memristor device                                    | 26  |

| Figure 16. Typical I-V curves and modeling of memristor device               | 27  |

| Figure 17. Vector-by-matrix multiplier based on ESF-1 memory cells           | 29  |

| Figure 18. Flowchart of the proposed tuning algorithm                        | 29  |

| Figure 19. Tuning results of ESF-1 memory cells                              | 30  |

| Figure 20. Switching dynamics of ESF-1 memory cells                          | 32  |

| Figure 21. Device-to-device variations of ESF-3 memory cells                 | 33  |

| Figure 22. Tuning results of ESF-3 memory cells                              | 34  |

| Figure 23. Analog vector-by-matrix multiplication in a crossbar                  | . 36 |

|----------------------------------------------------------------------------------|------|

| Figure 24. Preliminary results for a ESF-1 vector-by-matrix multiplier           | . 38 |

| Figure 25. Fabricated $4 \times 4$ ESF-1 analog vector-by-matrix multiplier      | . 39 |

| Figure 26. Real outputs of $4 \times 4$ ESF-1 analog vector-by-matrix multiplier | . 40 |

| Figure 27. The vector-by-matrix multiplication scheme of ESF-3 technology        | . 41 |

| Figure 28. Real outputs of ESF-3 analog vector-by-matrix multiplier              | . 42 |

| Figure 29. The relative error of ESF-3 multiplier at various temperatures        | . 43 |

| Figure 30. Pattern classifier's network architecture                             | . 46 |

| Figure 31. Pattern classifier's circuit diagram                                  | . 49 |

| Figure 32. A micrograph of the chip and its area breakdown                       | . 51 |

| Figure 33. Pattern classifier's weight export statistics                         | . 52 |

| Figure 34. Classification of all 10,000 MNIST test set                           | . 55 |

| Figure 35. Pattern classifier's simulated classification fidelity                | . 56 |

| Figure 36. Pattern classifier's physical performance.                            | . 57 |

| Figure 37. Proposed perceptron implementation with nonlinear synaptic weights    | . 61 |

| Figure 38. Fabricated ESF-1 10 x 10 memory array                                 | . 62 |

| Figure 39. Results of the proposed architecture with exponential weights         | . 62 |

| Figure 40. Conventional Hopfield network implementation of a 4-bit ADC           | . 65 |

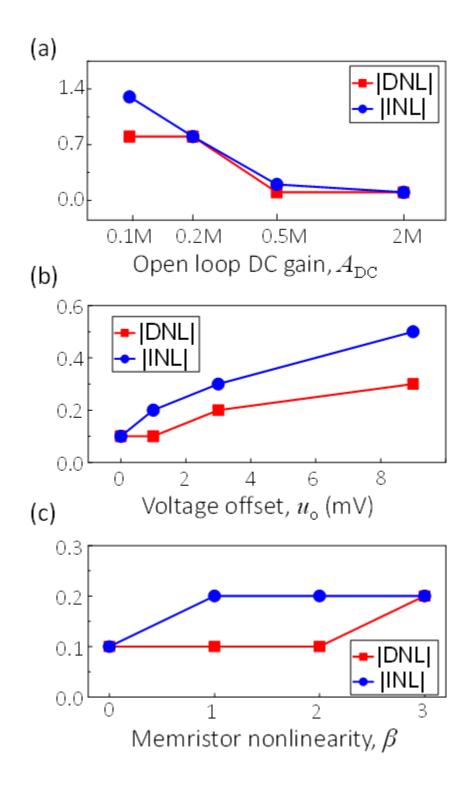

| Figure 41. Performance sensitivity of a 4-bit Hopfield network ADC               | . 74 |

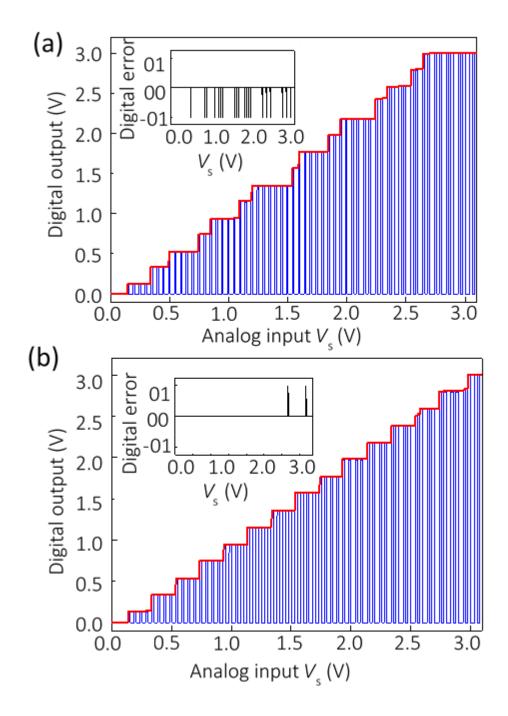

| Figure 42. Simulation results for a 4-bit Hopfield network ADC                   | . 75 |

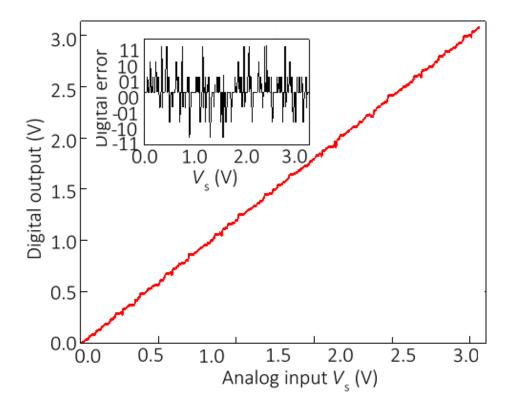

| Figure 43. Simulation results for an 8-bit Hopfield network ADC                  | . 76 |

| Figure 44. Experimental results for the optimized 4-bit Hopfield ADC             | 77   |

## I. Introduction

In the past few years, neuromorphic computing has advanced greatly in solving cognitive problems such as pattern recognition, speech translation, topic classification and so on. Among diverse neuromorphic networks, deep learning approach is a important subfield for its success in both commerce and academia [1-3]. In general, deep learning neuromorphic networks consist of a large number of processing layers which contain millions of weights (called synapses) connected simple processors called neurons [4]. Despite of various deep learning architectures such as multilayer perceptron, convolutional neural network and recurrent neural networks, all architectures are stack of processing layers which perform linear or nonlinear transformations of previous layer's outputs. The concise and uniform structure of deep learning neuromorphic networks along with its outstanding performance in tremendous domains will allow a revolutionary technological leap toward outperforming conventional complimentary metal-oxide semiconductor (CMOS) technology [5].

Technology breakthroughs and designs are expected in implementing neuromorphic systems, due to the huge difference from traditional Von Neumann computational architecture. There is a booming of approaches to implement deep neural networks models with distinct analog, digital, mixed-mode analog/digital VLSI, and software systems [6 - 14]. For example, the rapid computational capability evolving in graphics processing units (GPUs) facilitates the scaling up of neuromorphic networks to an extent that they can accomplish certain applications with configurable features. However, GPUs are relatively expensive, area costly and prohibitively power hungry [15]. Neuromorphic application-specific integrated circuits (ASICs) have shown their speed and power advantages over

GPUs with the same technology node [14, 16], the advances ASICs achieved is still not adequate. To resolve previous mentioned contemporary issues, dedicated hardware approaches are needed to utilize the similarities between Silicon and neurobiology, e.g., memory, to maximize the potential of neuromorphic architectures [17].

The concept of using nonvolatile memories for signal processing at relatively low precision requirements, for example analog and mixed-signal neuromorphic networks, far superior to digital circuits of the same functionality in speed and energy efficiency, is at least 30 years old [18, 19]. Limited by the technology, precision handicap was one of the major challenges preventing analog computation's prevailing back then. Fortunately, with the technology developments, neuromorphic networks are scaled up, obtaining high tolerance of their operation to synaptic weight variations, and hence the precision requirement in neuromorphic computing is proven to be as low as several bits or even binary [20 - 27]. Without the precision wall, analog computing is the key to break the power, area and cost bottleneck [17]. Benefitting from the inherent similarities between analog circuits and biological systems, many theoretical and experimental works further confirm the advantages of analog approach [28-31]. Moreover, since there is storage requirement for a tremendous number of synapses inside any practical neuromorphic networks, utilizing computation in memory would be both efficient and straight forward [32, 33]. Recent works [27, 34 - 35] have shown that such circuits, utilizing nanoscale devices, improves the neuromorphic network performance dramatically, leaving far behind both their digital counterparts and biological prototypes, and approaching the energy efficiency of the human brain.

The key component of such mixed-signal neuromorphic networks is a device with adjustable (tunable) conductance - essentially an analog nonvolatile memory cell,

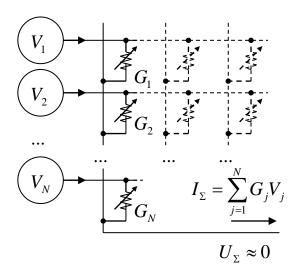

mimicking the biological synapse. There have been significant recent advances in the development of nanoscale nonvolatile memories, such as ReRAMs, MRAM, PCRAM, FeRAM, NOR Flash memories, NAND Flash memories and 3D ReRAMs – for a review, see, e.g., Refs, 36 - 42. In particular, those emerging memories have already been used to demonstrate small neuromorphic networks [43 - 55]. The background of further advantages among different analog approaches is the fact that in memory based neuromorphic circuits, the vector-by-matrix multiplication, i.e. the key operation performed at signal propagation through any neuromorphic network, is implemented on the physical level, in a resistive crossbar circuit, using the fundamental Ohm and Kirchhoff laws.

However, for most of the emerging memories, their fabrication technology is still in much need for improvement and not ready yet for the large-scale integration, which is necessary for practically valuable neuromorphic networks. Up until recently, such devices were implemented mostly as floating-gate "synaptic transistors" [15, 56], which may be fabricated using the standard CMOS technology. Flash memory device has inherently adjustable conductance and the advancing to three-dimensional integration with higher density makes it more appealing for neuromorphic applications [57]. Recently some rather sophisticated neuromorphic systems were demonstrated [15, 58] using this approach. However, synaptic transistors have relatively large areas ( $\sim 10^3 F^2$ , where F is the minimum feature size), leading to larger time delays and energy consumption [17].

In this thesis, we mainly use the highly optimized, nanoscale, nonvolatile floating-gate memory cells which are used in the recently developed embedded NOR flash memories [59]. These cells are quite suitable to serve as adjustable synapses in neuromorphic networks, provided that the memory arrays are redesigned to allow for individual, precise adjustment of the memory state of each device. Recently, such modification was performed

[60, 61] using the 180-nm ESF1 embedded commercial NOR flash memory technology of SST Inc. [59], and, more recently, the 55-nm ESF3 technology of the same company [62], with good prospects for its scaling down to at least F = 28 nm. (The last number is just slightly worse than the expected size of the emerging nonvolatile memories with transistor-based selectors.) Though such modification nearly triples the cell area, it is still at least an order of magnitude smaller, in terms of  $F^2$ , than that of synaptic transistors [17].

As a key step towards area and power efficient neuromorphic network, small vector-by-matrix multipliers are separately fabricated and tested based on redesigned 180-nm ESF1 and 55-nm ESF3 arrays [60, 62]. The demonstrated vector-by-vector multipliers are operating in low-power subthreshold mode, with gate coupling of array cells to the input (peripheral) cells. In order to reduce the temperature drift, pertinent to the subthreshold operation of the cells, differential versions of multipliers are implemented and characterized to minimize the output signal drift.

The main result reported in this thesis is the first successful use of previous mentioned approach for the experimental implementation of a mixed-signal neuromorphic network performing high-fidelity classification of patterns of the standard MNIST benchmark, with record-breaking speed and energy efficiency [63]. Hardware constrains aware designs are applied throughout the implementation especially when training the network in software before importing into the fabricated chip.

Another prototype reported in this thesis explores the implementation of synapses with the emerging, very promising memristor devices to build a recurrent artificial neural network called Hopfield analog-to-digital (ADC) network [64].

## **II. Memory Elements**

The key component of the most advanced analog computing implementations is a nanodevice with adjustable conductance – essentially an analog nonvolatile memory cell, which could mimic synaptic transmission function by multiplying signal from the input neuron (e.g. encoded as voltage applied to the memory device) by its analog weight (device conductance) and passing the product (the resulting current) to the output. Such functionality enables very dense, fast, and low power implementation of dot-product computation, the most common operation in many artificial neural networks. However, there is a particular challenge for utilizing analog nonvolatile memory cell. The challenge is that the synapse is an analog memory element, and, e.g., at a lot of occasions, 5-bit precision is required for convolutional networks [27, 65]. The most promising analog memory devices are memristive device and floating gate device. The former one is an ideal candidate with super density while the later one is a more practical, mature technology for implementing large scale neural networks for now.

## A. 180-nm ESF1 Floating-Gate

In this section, we have modified a commercial NOR flash memory array to enable high-precision tuning of individual floating-gate cells for analog computing applications. The modified array area per cell in a 180-nm process is about 1.5 µm². While this area is approximately twice the original cell size, it is still at least an order of magnitude smaller than in the state-of-the-art analog circuit implementations. The new memory cell arrays have been successfully tested, in particular confirming that each cell may be automatically tuned, with ~1% precision, to any desired subthreshold readout current value within an almost three-orders-of-magnitude dynamic range, even using an unoptimized tuning algorithm.

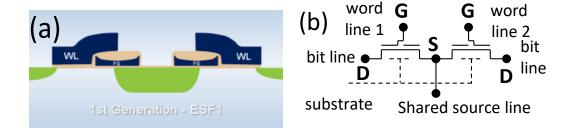

Fig. 1. SST's ESF-1 technology [59]: (a) schematic cross-section of a supercell, (b) its equivalent circuit, and (c) TEM cross-section image of one half of the supercell implemented in a 180-nm process.

#### 1. Device Characterization

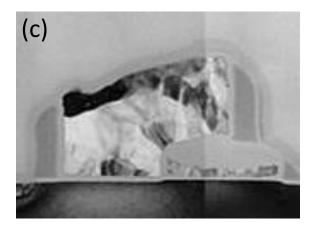

The 180-nm NOR memory array consists of "supercells" (Fig. 1). Each supercell is a common-source assembly of two floating-gate memory cells with a highly asymmetric structure: the control gate (usually connected to a "word" line) overlaps the drain region of cell's MOSFET transistor, while being separated from its source region by the floating gate. Because of that, the direct effect of the gate voltage on the process of electron emission by the source is very small. This is evident from the readout characteristics of the cell, shown in Fig. 2: at  $V_{\rm DS} > 0$ , when the source-to-drain current is due to the electron emission from the source, a large gate voltage is necessary to open the transistor of a fully programmed cell (with negatively charged floating gate). On the other hand, at  $V_{\rm DS} < 0$ , when electrons are

emitted by transistor's drain, the effect of control gate voltage on the current is much stronger, while that of the floating gate charge is much weaker.

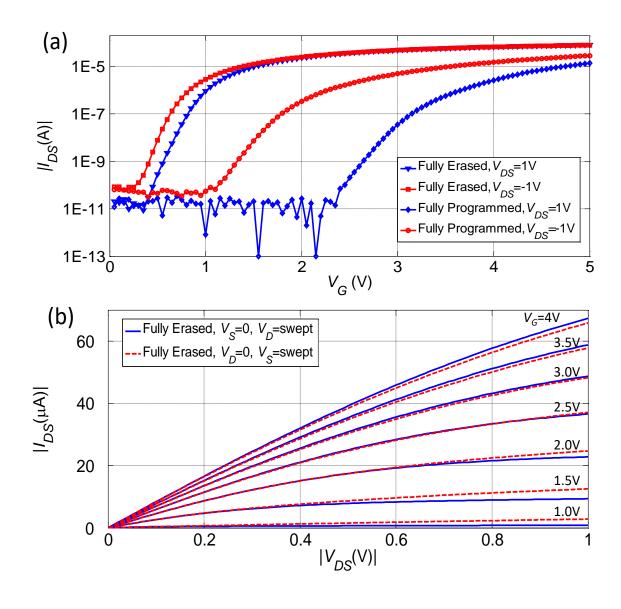

Fig. 2. Readout characteristics of 180-nm ESF-1 memory cells: Drain-source current as a function of (a) gate and (b) drain-source voltage.

Fig. 3. Analog tuning of 180-nm ESF-1 memory cells, characterized by the change in source-to-drain current  $I_{DS}$  (as measured at  $V_G = 2.5 \text{V}$ ,  $V_D = 1 \text{V}$ , and  $V_S = 0 \text{V}$ ) under effect of applied voltage pulses: (a, b) gradual programming of an (initially erased) device with 5- $\mu$ s source voltage pulses of various amplitudes  $V_S$ ; (c, d) gradual erasure of an (initially programmed) device with gate voltage pulses of various amplitudes  $V_G$  and durations  $\Delta t$ .

The same structure asymmetry affects the switching dynamics of the cell (Fig. 3). During the "programming" process, the negative charge of the floating gate may be increased very fast using very effective hot-electron injection from the source area of transistor's channel, while the simplest way to decrease it (and hence "erase" the cell) is via the Fowler-Nordheim tunneling of electrons from the floating gate to the control gate, by applying a rather high voltage (~ 11 V) to the latter electrode.

Our network design uses energy-saving gate coupling [17, 66, 67] of the peripheral and array cells, which works well in the subthreshold mode, with a nearly exponential dependence of the drain current  $I_{DS}$  of the memory cell on the gate voltage  $V_{GS}$  (Fig. 4):

$$I_{\rm DS} \approx I_0 \exp\left\{\beta \frac{V_{\rm GS} - V_t}{V_{\rm T}}\right\},$$

(1)

where  $V_T$  is a threshold voltage depending on the memory state of the cell (physically, the electric charge of its floating gate),  $V_T \equiv k_B T/e$  is the voltage scale of the thermal excitations, equal to ~26 mV at room temperature, while  $\beta < 1$  is the dimensionless subthreshold slope  $d(\ln I_{DS}/dV_{GS})$ , measured in the units of  $V_T$ , and characterizing the efficiency of the gate-to-channel coupling. As the inset in Fig. 4d shows, in the ESF1 cells this slope stays relatively constant in a broad region of memory states – a feature enabling the gate-coupled circuit operation. (For lower  $V_t$ , the slope becomes higher, apparently due to the cell's split-gate design – see Fig. 1a.)

Fig. 4 The grey-shaded region shows the subthreshold conduction region; the currents below  $I_{DS} = 10$  pA (the level shown with the dashed line) are significantly contributed by leakages in the experimental setup used for the measurements. The inset shows the extracted slope of this semi-log plot, measured at  $I_{DS} = 10$  nA, as a function of the memory state (characterized by the corresponding gate voltage).

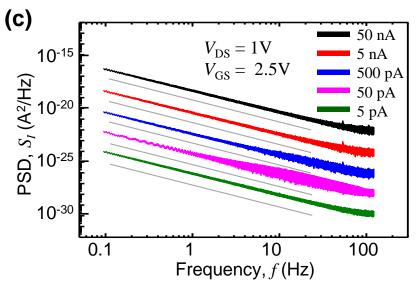

Fig. 5. (a) Results of analog retention measurements for several memory states, performed in the gate-coupled array configuration, and (b) the average relative variation of the currents during the same time interval. The inset shows the equivalent circuit of the used gate coupling. Each point on panel (a) is an average over 65 samples taken within a 130 ms period. (c) Spectral density of cell current's noise measured at room temperature; the gray lines are just guides for the eye, corresponding to  $S_I$  $\propto 1/f^{1.6}$ .

With the requirement to keep the relative current fluctuations (Fig. 5b) below 1%, the dynamic range of the subthreshold operation is about five orders of magnitude, from ~10 pA to ~300 nA, corresponding to the gate voltage swing of ~1.5 V.

The ESF1 flash technology guarantees a 10-year digital-mode retention at temperatures up to 125°C [59]. Our experiments have shown that these cells also feature at least a-few-days analog-level retention, with very low fluctuations of the output current – see Fig. 5.

#### 2. Array Design

The top row of Fig. 6 shows the usual structure of the NOR flash memory and its programming/erasure voltage protocols, employing these properties of the SST cells. In this architecture, cells of the same row share transistor source and control gate ("word") lines, while transistor drains of all cells of the same column are connected to the same "bit" line. Fig. 6a shows the set of applied voltages used for programming of the top left cell, while avoiding state disturb in all other cells. In particular, a positive bias  $V_D^{P'} > 2V$ , applied to all unselected bit lines, inhibits unintentional hot-electron injection in all unselected cells, including type-A half-selected cells (sitting on the selected word line). Also, grounding of unselected word lines guarantees the absence of disturb processes (such as the back Fowler-Nordheim tunneling) in all unselected cells including half-selected cells of type B (sharing the source voltage with the selected cell). As Fig. 3a indicates, the same programming protocol, only with pulsed source voltage and slightly modified voltage values, allows analog programming of the selected cell, also without disturbing the half-selected cells, regardless of their charge state.

Unfortunately, in this memory architecture the opposite process of cell erasure (Fig. 6b) is much less controllable. Namely, the fully selected cell and the type-C half-selected cell

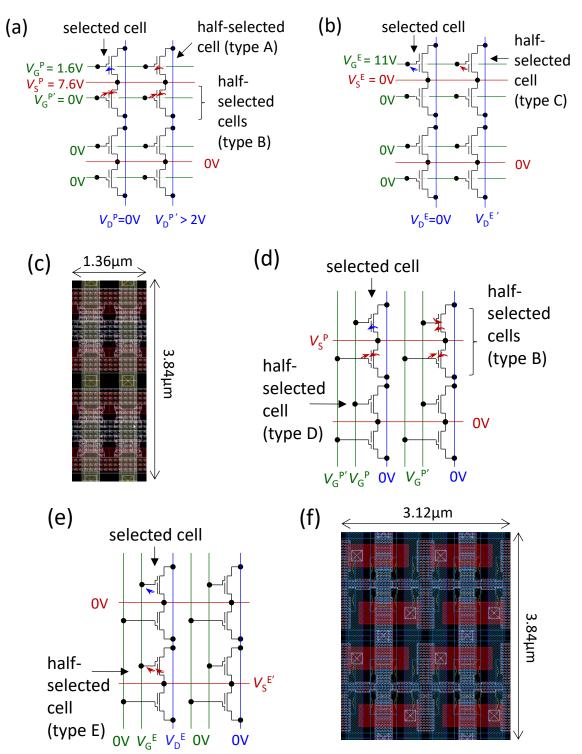

Fig. 6. Floating gate recharging effects: (a, b) – in the original SST array (c), and (d, f) – in the array with modified routing (f), on the example of a  $2\times2$  supercell array fragment. Voltages shown on panels (a, d) correspond to programming of the top left cell, while those on panels (b, e), to its erasure. Blue and red arrows show, respectively, the useful and undesirable recharging processes. Line colors are for clarity only.

share their gate and source voltages, and due to the cell structure (Fig. 1) the process responsible for erasure (the Fowler-Nordheim tunneling of electrons from the floating gate to the control gate) is only weakly affected by the drain voltage  $V_D$  – the only voltage which may be different for these two cells. (The possible increase of  $V_D^{E'}$  is limited by the onset of large drain-to-source current.) For digital applications, this feature is not a handicap, because in flash memories all cells of the same row are erased simultaneously. However, in analog applications it is highly desirable to perform not only a gradual programming of each cell, but also a gradual erasure of each cell without disturbing its neighbors. Our detailed measurements (see, e.g., Fig. 3c, d) have shown that in the baseline architecture (Fig. 6a-c) the latter operation is impossible for any bias voltage set.

To resolve this problem, we have modified the array structure (without changing the optimized cell fabrication technology) as shown in the bottom row of Fig. 6, i.e. by rerouting the gate lines in the "vertical" direction, i.e. perpendicular to the source lines. A straightforward analysis of the data shown in Figs. 2 and 3 shows that the new design resolves the half-selected cell disturb problem, by using the applied voltage protocol shown in Fig. 6d, e, with  $V_G^E \approx 8.5 \text{V}$ ,  $V_S^{E'} \approx 3 \text{V}$ , and  $V_D^E \approx 3 \text{V}$ .

Indeed, for the programming operation, most of the half-selected cells are of the type B, while the disturb in type D cells, with  $V_G^{P'} = -1V$ , is even less problematic. For the erase operation, the new gate line routing enables taking advantage of the very strong nonlinearity of possible Fowler-Nordheim and hot-electron tunneling currents (as functions of, respectively, the drain and source voltages), to completely inhibit these effects in all unselected cells including half-selected cells of type E.

The SST cell array with the architecture shown in Fig. 6d, e has been designed, fabricated (so far in the 180-nm technology of SST, Inc.) and successfully tested. Fig. 6f

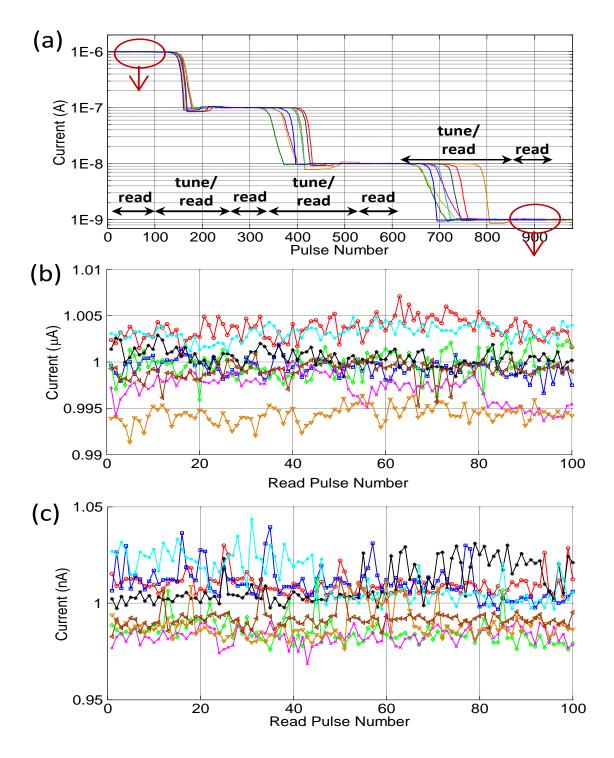

Fig. 7. High-precision tuning of cells of the modified memory: (a) All cells being tuned sequentially to 1  $\mu$ A, 100 nA, 10 nA, and 1nA readout currents (as measured at  $V_G = 2.5 \text{V}$ ,  $V_D = 1 \text{V}$ ,  $V_S = 0 \text{V}$ ); (b, c) zoom-in on the readout of the first and the last of the tuned states, to highlight the current variations due to intrinsic device noise. On all panels, each point represents the current average over a 10-ms time interval.

shows the layout of the new array. Its area per cell is 2.3 times larger than the original one (Fig. 6c) due to the additional real estate needed to accommodate two gate lines for each cell column.

To verify that the new array architecture enables a full inhibition of half-select disturb effects, we have performed a series of experiments, tuning all 8 cells in a 2×2 supercell array, one by one, to pre-selected goal values with a ~1% precision (Fig. 7), using a simple, fully automated feedback procedure that had been originally developed for tuning memristive devices [46, 68]. Its algorithm consists of alternating "tune" (either program or erase) and "read" pulses applied to the selected device. Every read measurement determines the necessary direction of the next tune operation, i.e. whether program or erase pulses are needed. If a read measurement shows that the desired value has been overshot, the tuning pulse polarity is changed. The tuning procedure stops when the device has reached the desired analog state with the pre-specified precision [46, 68].

In the particular series of experiments shown in Fig. 7, the initial erase was performed with a 10-ms, 10-V gate pulse, keeping  $V_D = V_S = 0$ , while the initial programming, with a 5- $\mu$ s, 9-V source pulse, keeping  $V_D = 0$ V and  $V_G = 1.6$  V. The gradual programming was done using 5- $\mu$ s source voltage pulses with an initial amplitude of 4.5 V, which was then ramped up to 8V in 50-mV steps, while applying dc voltages  $V_G^P = 1.6$ V,  $V_G^{P'} = -1$ V and keeping other lines grounded. The gradual erase was performed using 0.6-ms gate pulses with an initial amplitude of 5V, which was then increased to the maximum value of 8.5V, also in 50-mV steps, while applying dc voltages  $V_D^E = 2.7$ V,  $V_S^E = 0$ V,  $V_S^{E'} = 2.7$ V, and keeping other lines grounded. (This choice of voltages is likely suboptimal and may be improved to increase tuning speed.)

#### B. 55-nm ESF3 Floating-Gate

The advanced commercial 55-nm ESF3 technology of the same company [59], with good prospects for its scaling down to at least F = 28 nm. The modified arrays enable high-precision individual analog tuning of each cell, with sub-1% accuracy, while keeping the highly-optimized cells, with their long-term state retention, intact. The array has an area of 0.33  $\mu$ m<sup>2</sup> per cell, and is at least one order of magnitude denser than the reported prior implementations of nonvolatile analog memories.

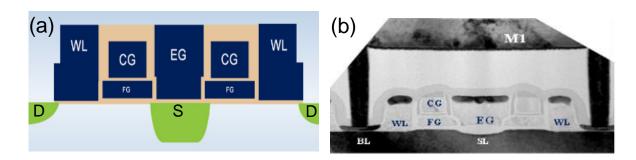

Fig. 8. SST's 55-nm ESF3 NOR flash memory cells: (a) schematic view, and (b) TEM image of the cross-section of a "supercell" incorporating two floating-gate transistors with a common source (S) and erase gate (EG) [59].

## 1. Device Characterization

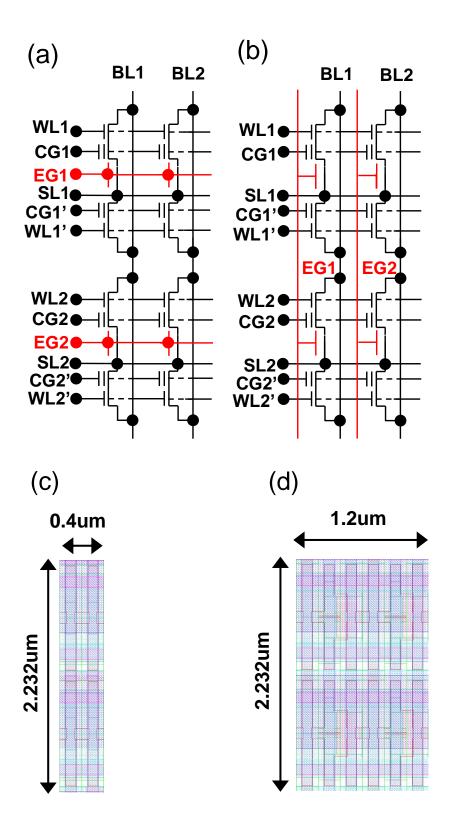

The ESF3 NOR flash memory is based on "supercells" with two floating-gate transistors sharing the source (S) and the erase gate (EG), but are controlled by different word-line (WL) and coupling (CG) gates - see Fig. 8. In the original ESF3 memory arrays, the cells are connected as Fig. 9a shows, with six row lines per supercell, connecting transistor sources, erase gates, coupling gates, and word-line gates, while each column has only one ("bit") line connecting transistor drains (D). In this array topology, each cell may be programmed individually, by hot-electron injection into its floating gate. For that, the voltage on the source line (SL in Fig. 9) of the cell's row is increased to 4.5 V (while those in other rows are kept at 0.5 V), with the proper column selected by lowering the bit line (BL) voltage to

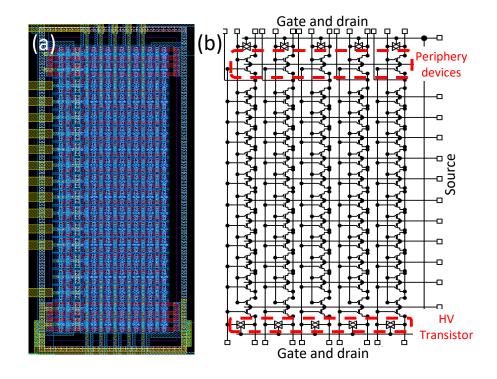

Fig. 9. (a, c) Original and (b, d) modified circuitry and layout for 4-supercell ESF3 55-nm memory array.

0.5 V (while keeping all other bit line voltages above 2.25 V). This process works well for providing proper digital state, with 1- or even 2-bit accuracy. However, it is insufficient for cell tuning with analog (say, 1%) precision. Unfortunately, the reverse process ("erasure"), using the Fowler-Nordheim tunneling of electron from the floating gates to the erase gates, may be performed, in the original arrays, only in the whole row, selected by applying a high voltage of ~ 11.5 V to the corresponding erase gate line (with all other EG voltages kept at 0 V). So, these arrays do not allow for a precise analog cell tuning, which unavoidably requires an iterative, back-and-forth (program-read-erase-read-program...) process, with the run-time result control. The required modification details will be discussed in the next section.

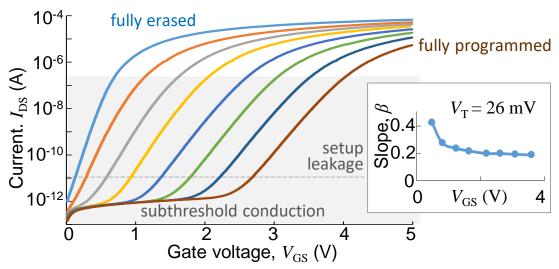

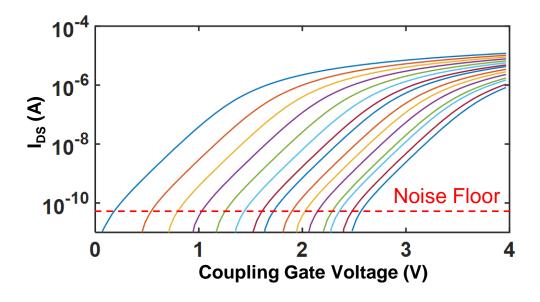

Fig. 10. Drain-source current of a modified ESF3 cell as a function of the coupling gate voltage, for several different memory states.

The ability to tune the floating gate cells of the modified arrays continuously is illustrated in Fig. 10 which shows the readout current as a function of the coupling gate voltage for a selected equidistant series of cell states. These semi-log plots have wide quasi-

linear segments, corresponding to the nearly-exponential behavior of the current in the subthreshold region. In the current range from 100 pA and 30 nA, the subthreshold slope factor n, defined by the well-known relation  $I \propto \exp\{qV_{\text{CG}}/nk_{\text{B}}T\}$ , varies only from 5 to 5.1 for all the 15 states shown in Fig. 10. This low variability of n enables the implementation of highly linear signal transfer in gate-coupled current mirrors using these cells [17].

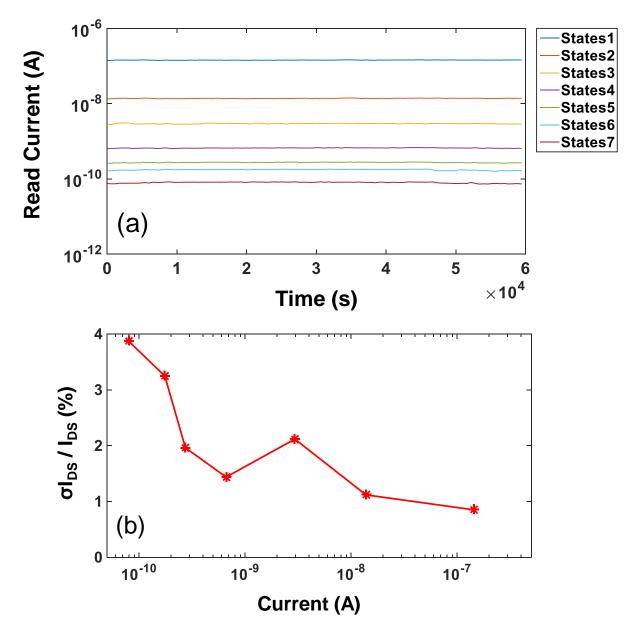

Fig. 11. (a) Retention measurements for several cells in different memory states at 85°C, and (b) the average relative variation of the readout currents during this time interval.

The ESF3 flash technology guarantees a 10-year digital-mode retention at temperatures up to 125°C [59]. To explore its analog mode retention, we have programmed 7 memory cells to 7 different states from around 100 pA to 100 nA covering the whole subthreshold region, and then were continuously monitoring their output current within a day under 85 °C as shown in Fig. 11a. Each point on this panel is an average over 128 samples taken during 16 ms periods. Fig. 11b shows the relative r.m.s. variation of the current during the measurement period for the 7 states shown in Fig. 11a. For larger currents the variation is below 1%, increasing to ~4% only at the lower boundary of the range.

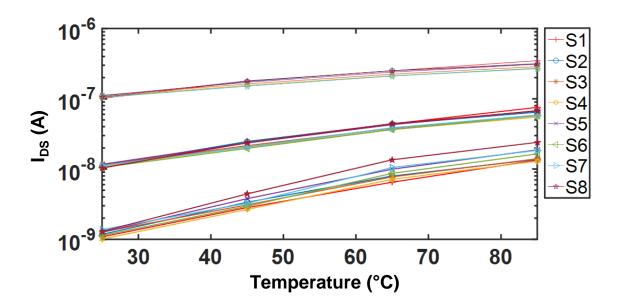

Fig. 12. Temperature dependence of drain-source current for several memory cells with different memory states, with the initial readout currents close to 1 nA, 10 nA and 100 nA.

In order to fairly characterize the temperature dependence of the cell output current in the subthreshold region, we have programmed 8 cells to 8 different states, equally spread over the useful dynamic range. Then, in 3 different experiments, appropriate coupling gate voltages were applied to each cell, to make the readout currents of them all equal to, sequentially, 1 nA, 10 nA and 100 nA at 25 °C. After that, temperature was ramped up from  $25^{\circ}$ C all the way to  $85^{\circ}$ C, and the readout current of each cell was monitored. Fig. 12 shows the results of these 3 experiments. In accordance with our expectations (and the measured values of n), the currents increased significantly – more than by an order of magnitude for the lowest initial current. Though in the gate-coupling scheme (see below) this changes are mostly compensated by similar changes in the input (peripheral) transistors, this fact still shows that the temperature sensitivity of the subthreshold current requires special attention.

## 2. Array Design

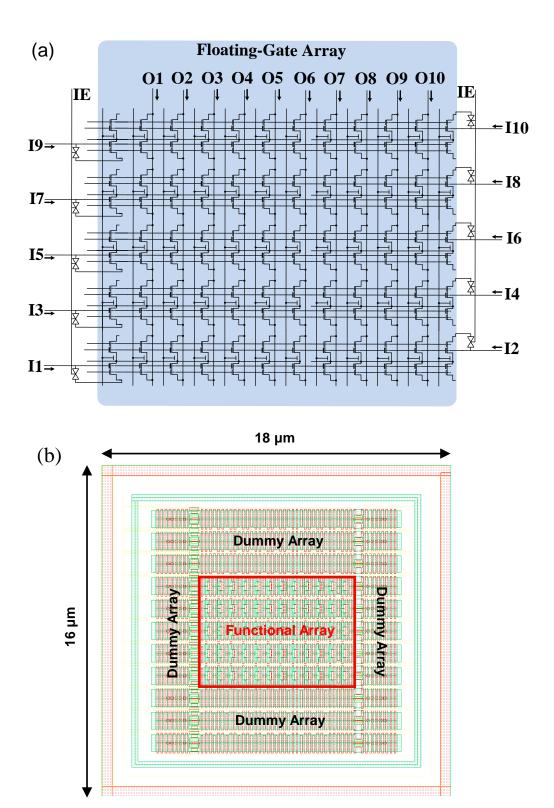

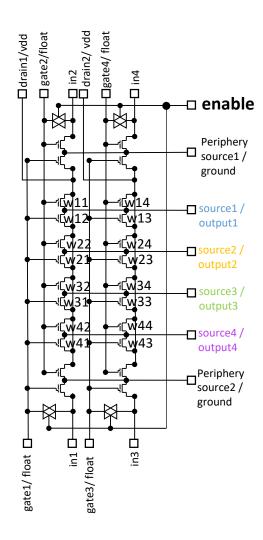

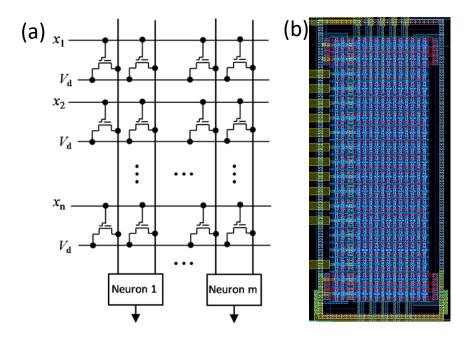

We have modified the ESF3 memory arrays as shown in Fig. 9b, by connecting the erase gates of all cells of one column with an additional line, while eliminating the row lines connecting these gates. (Note that this redesign is different from the one performed by our group earlier [60] with the 180-nm ESF1 technology, because of a different structure of its supercells.) Fig. 13 shows our test 10×10 modified ESF3 cell array. The peripheral cells designed for multiplier purpose are located in the additional columns on the left and the right from the basic array. (Two columns are necessary because with the ESF3 supercell structure we can use only one half of each supercell as the peripheral cell.)

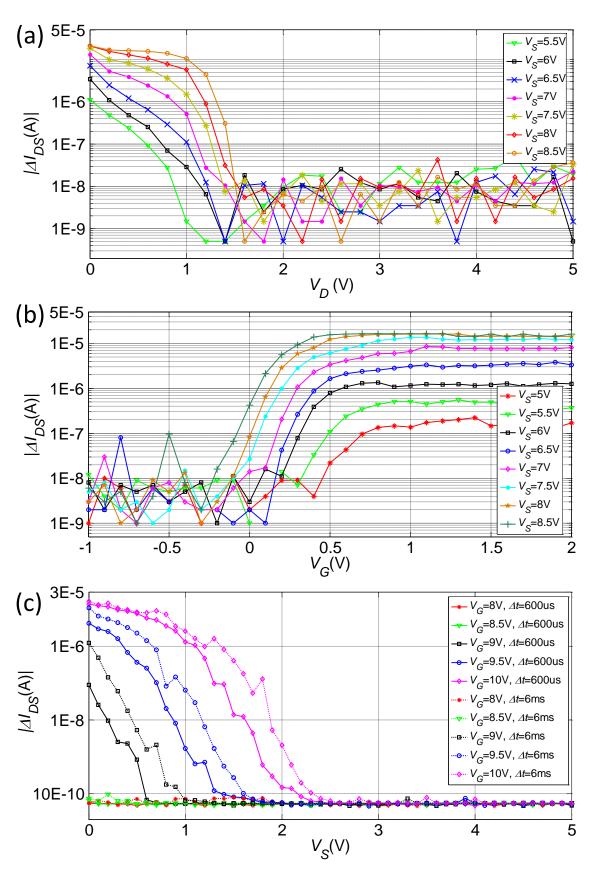

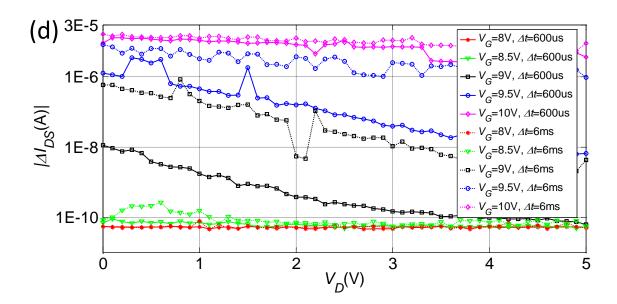

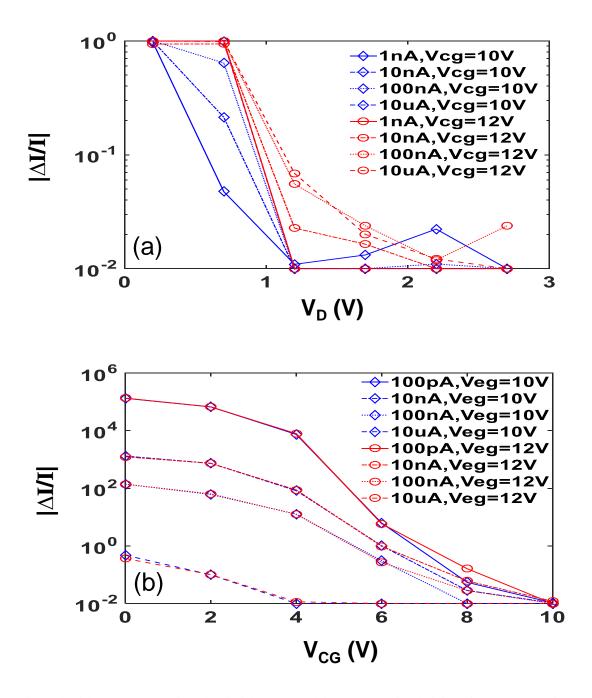

In the modified arrays, the analog hot-electron programming of each cell may be performed by applying 10 µs pulses of a fixed amplitude of 4.5 V to the source line of the corresponding row. In this process, the proper column is selected by applying a positive voltage ~4 V between the erase-gate and bit lines, while keeping this voltage negative for all un-selected columns [69]. Fig. 14a documents the inhibition of the unwanted programming process in a half-selected cell at the increase of the bit-line (i.e. drain) voltage.

Fig. 13. Gate-coupled vector-by-matrix multiplier based on a  $10\times(10+2)$  array of ESF3 floating-gate cells, together with auxiliary pass-gates (which are disabled during tuning with IE signal): (a) schematics; (b) layout for 55-nm fabrication.

Fig. 14. (a) Programming inhibition and (b) erasure inhibition in the transistors of half-selected cells. Unless specified otherwise, the shown readout (source-to-drain) currents have been measured at  $V_{WL} = 2.5 \text{ V}$ ,  $V_{CG} = 2.5 \text{ V}$ ,  $V_D = 1 \text{ V}$ ,  $V_S = 0 \text{ V}$ , and  $V_{EG} = 0 \text{ V}$ .

The opposite process of individual analog erasure via the Fowler-Nordheim tunneling is now also possible, by using the new column lines to apply high-amplitude (11.5 V), 0.5 ms pulses to the erasure gates of the selected column. The proper row is selected by grounding

the corresponding coupling gate line, while keeping a high voltage (+8 V) on these lines of unselected rows. As Fig. 14b shows, such a positive bias inhibits the Fowler-Nordheim tunneling in half-selected cells, due to a relatively high capacitance between the coupling gate and the floating gate of the same transistor [70].

Due to the line rerouting, the array area per cell has nearly tripled – cf. Figs. 9c and 9d. However, even with this increase the area is still as small as  $0.33 \mu m^2$ , i.e. ~  $110 F^2$ , much smaller than in any other design we are aware of.

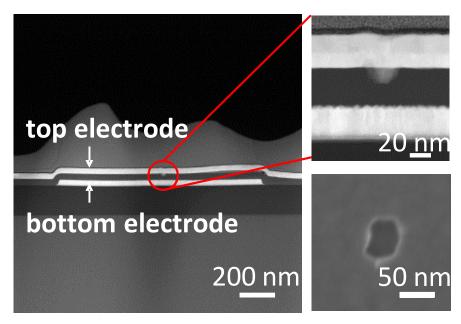

#### C. Memristive Device

Another synapse candidate with high density is nonvolatile memristive devices. In their simplest form, memristors are two-terminal passive elements, the conductance of which can be modulated reversibly by applying electrical stress. Due to the simple structure and ionic nature of their memory mechanism, metal-oxide memristors have excellent scaling prospects, often combined with fast, low energy switching and high retention [36]. Many metal oxide based memristors can also be switched continuously, i.e. in analog manner, by applying electrical bias (current or voltage pulses) with gradually increasing amplitude and/or duration. The Pt/TiO<sub>2-x</sub>/Pt memristive device we fabricated is shown Fig.15.

#### 1. Device Characterization

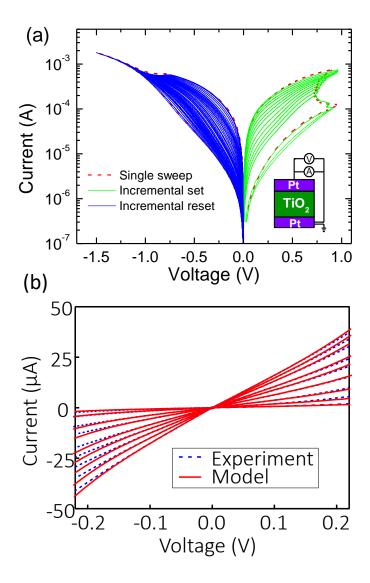

Fig. 16a shows typical continuous switching *I-V*s for the considered Pt/TiO<sub>2-x</sub>/Pt devices [71]. The devices were implemented in "bone-structure" geometry with an active area of ~1 μm<sup>2</sup> using the atomic layer deposition technique. An evaporated Ti/Pt bottom electrode (5nm/25nm) was patterned by conventional optical lithography on a Si/SiO<sub>2</sub> substrate (500 μm/200 nm, respectively). A 30 nm TiO<sub>2</sub> switching layer was then realized by atomic layer deposition at 200°C using Titanium Isopropoxide (C<sub>12</sub>H<sub>28</sub>O<sub>4</sub>Ti) and water as precursor and

Fig. 15. TEM images of 50-nm-thick titanium dioxide devices with e-beam defined protrusion

reactant, respectively. A Pt/Au electrode (15nm/25nm) was evaporated on top of the TiO<sub>2</sub> blanket layer, and the device was finally rapidly annealed at 500° C in an N<sub>2</sub> and N<sub>2</sub>+O<sub>2</sub> atmosphere for 5 minutes to improve the crystallinity of the TiO<sub>2</sub> material. Details of the fabrication and characterization of the considered memristors are given in Ref. [67].

After programming the memristors to the desired resistance, it was important for their state to remain unchanged during operation of the Hopfield network, so to prevent any disturbance the voltage drop across them was always kept within the  $|V| \le 0.2V$  "disturbfree" range [71].

### 2. Modeling

The static *I-V* characteristics (i.e., those within disturb-free regime) for several different memory states are shown in Fig. 16b.

To assist SPICE simulation, the experimental I-V curves at small biases were fitted by the following static equation with a single memory state G:

$$I = GV + \beta(\alpha_1 G + \alpha_2 G^2 + \alpha_3 G^3)V^4.$$

(2)

where  $\beta = 1$ ,  $\alpha_1 = 14.7 \text{ V}^{-3}$ ,  $\alpha_2 = -5.9 \times 10^4 \Omega \text{V}^{-3}$ ,  $\alpha_3 = 1.5 \times 10^8 \Omega^2 \text{V}^{-3}$  for V > 0, and  $\alpha_1 = 34.6 \text{ V}^{-3}$ ,  $\alpha_2 = -1.9 \times 10^5 \Omega \text{V}^{-3}$ ,  $\alpha_3 = 3.65 \times 10^8 \Omega^2 \text{V}^{-3}$  for V < 0. As it is obvious from Equation 2, memory state *G* is simply a conductance (*I-V* slope) at zero voltage.

Fig. 16. (a) Typical I-V curves with current-controlled set and voltage-controlled reset switching for the considered Pt/TiO2-x/Pt memristors. (b) Modeling of static I-V curves at small disturb-free voltages for several different states.

# **III. High-Precision Tuning of Memory Elements**

Based on the detailed characterization of multilevel property (Figs. 4 and 10) in commercial NOR memory developed by SST Incorporation, it confirms the potential of flash memories as analog weights. Although for many analog computing applications, weights are typically changed infrequently so that tuning time and energy are of less importance, it is still essential to demonstrate feasibility of high precision tuning in flash memories and potential fast tuning methodology for large scale analog systems.

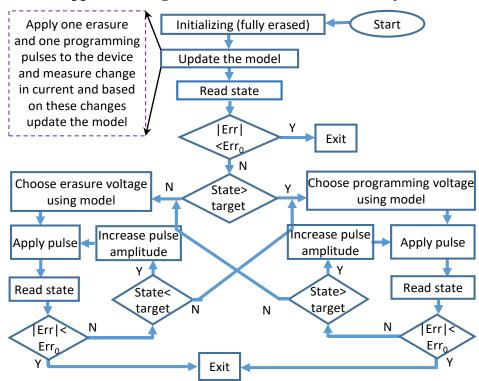

## A. Model-Based Fast Tuning of 180-nm ESF1 Floating-Gate Array

For ESF1 NOR flash memory, high-precision tuning experiments were performed within  $10\times10$  array of modified memory cells with an additional two rows of supercells included to implement gate-coupled vector matrix multiplier, which is the most critical component in neural network classifiers [35] (Fig. 17). The main idea of the algorithm (Fig. 18) is to use switching dynamics of the erasure and programming processes to calculate appropriate write pulse amplitudes. Based on the fitted behavior, a formula for the required voltage amplitude required to change the readout current (i.e. from current to desired state) is derived. Due to significant device-to-device variations in switching behavior, the parameters of the model are adjusted at the initial stage of the algorithm for the specific cell being tuned (Fig. 18). Due to significant cycle-to-cycle variations, the tuning cannot be implemented by applying a single pulse. Instead, the iterative scheme with the feedback is realized in which a sequence of a write (erase or program) and read pulses are applied in each iteration. Due to much steeper erase switching, governed by Fowhler-Nordheim tunneling as opposed to hot-electron injection for programming, overshooting at the programming stage was avoided by using smaller than ideal (i.e. determined by the model amplitude) program pulses. The

Fig. 17. Fabricated gate-coupled vector-matrix multiplier with  $(10+4) \times 10$  memory cells: (a) layout in 180-nm process, and (b) its schematics. The first and the last row of supercells are part of current mirror circuitry [66] that converts input currents into voltages that are applied to the gates of FG transistors in the array.

Fig. 18. Flowchart of the proposed tuning algorithm.

Fig. 19. (a) Measured versus target final states for 100 devices when taking into account half-select problem, and (b) tuning error as a function of the required number of tuning (erase & program) pulses. Panel a confirms that the disturbance of half-selected devices during tuning is negligible, while panel b shows that the number of tuning pulses grows exponentially with the tuning accuracy. (c) Average number of pulses and (d) tuning error for tuning 100 devices to different logarithmically-spaced target states.

optimal algorithm parameters leading to the smallest number of tuning pulses (i.e. faster tuning time) were found via exhaustive search. The tuning algorithm functionality was successfully verified in variety of conditions (Fig. 19). Naturally, the tuning was faster when tuning precision was low with roughly exponential increase in the number of tuning pulses required to get higher precision (Fig. 19b), which is similar to the tuning of phase change memory [72, 73].

### B. Tuning of 55-nm ESF3 Floating-Gate Array

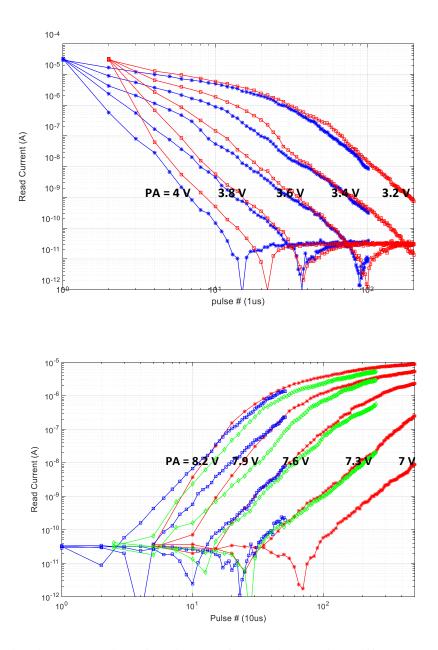

In order to gain continuous analog levels in memory cells and performing high precision and fast tuning for analog computing applications using 55-nm ESF3 flash memory, different amplitude and duration programming and erasing pulses will be applied. Considering the similar tuning strategy as fully automated feedback procedure in [61] for 180-nm reconfigured Flash memory, we explore the erasure dynamics by applying continuously pulses on EG with pulse amplitude (PA) of 7 V, 7.3 V, 7.6 V, 7.9 V, 8.2 V and pulse width (PW) of 10 us, 25 us, 50 us at a fully programmed device. As illustrated in Fig. 20 (a), we observe an exponential dependent on PA during erasure under subthreshold region. Moreover, the curves in different color are sited in good consistency on each other demonstrating total erasing time other than individual PW is essential for erasing. If we take advantage of that property, we can apply one long pulse instead of many short pulses when we have a model based on short pulse measurement [61]. In that way, we would save huge time on module communication for sending pulses. We observe similar programming dynamics when applying continuous programming pulses on source with PA of 3.2 V, 3.4 V, 3.6 V, 3.8 V, 4 V and PW of 2 us, 4 us at a fully erased device as shown in Fig. 20 (b). Exponential dependent on programming PA is observed. Similar to erasure process, matched curves on different color demonstrate a total programming time dependent property. That property could also be used to facilitate fast programming and save control module communication time.

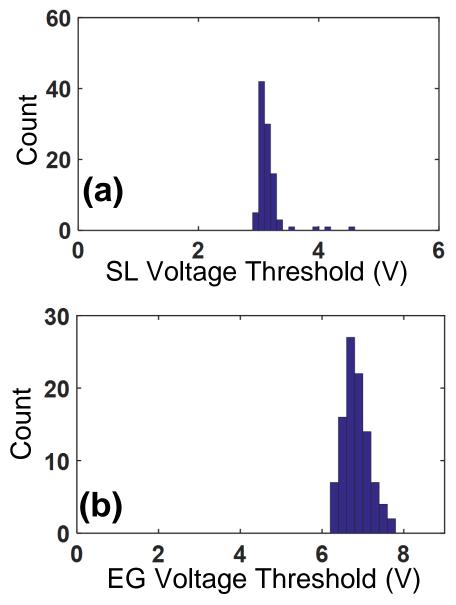

Since our proposed memory array will be used to implement large scale analog computing systems, it is crucial to understand device to device variations in switching dynamics for whole memory array tuning. Fig. 21 (a, b) illustrate the threshold voltage spread for programming and erasing in 100 memory cells respectively. The programming

Fig. 20. Switching dynamics of a single FG transistor with different pulse amplitude (PA) as well as different pulse width: (a) programming from fully erased state for each curve, (b) erasure from fully programmed state for each curve.

threshold voltage is defined as a source voltage that will change the device from fully erased state by 30% and the erasing threshold voltage is defined as an EG voltage that will change the device from fully programmed state by 30%. A very tight spread in programming threshold voltage with few outliers and relatively larger spread in erasing voltage are observed. That is mainly because hot electron injection process is less affected by the gate

oxide thickness compared with Fowler-Nordheim tunneling, and gate oxide thickness is severely affected when technology scaling down. As a result, a programming pulse is preferred when we are approaching the target during tuning when utilizing a model based tuning strategy [61].

Fig. 21. (a, b) Device-to-device variations for programming and erasing voltage thresholds for 100 devices.

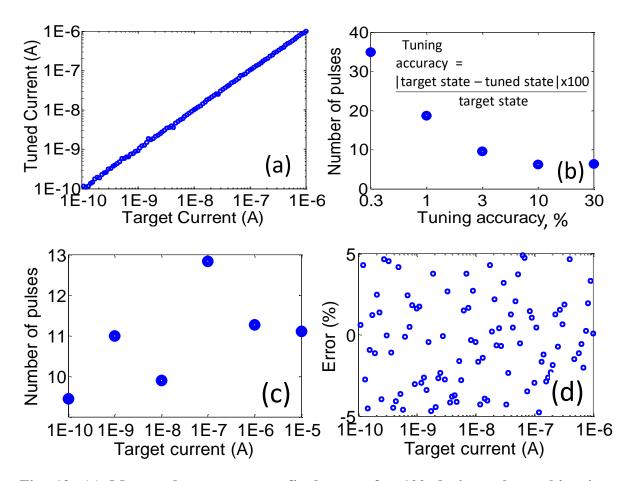

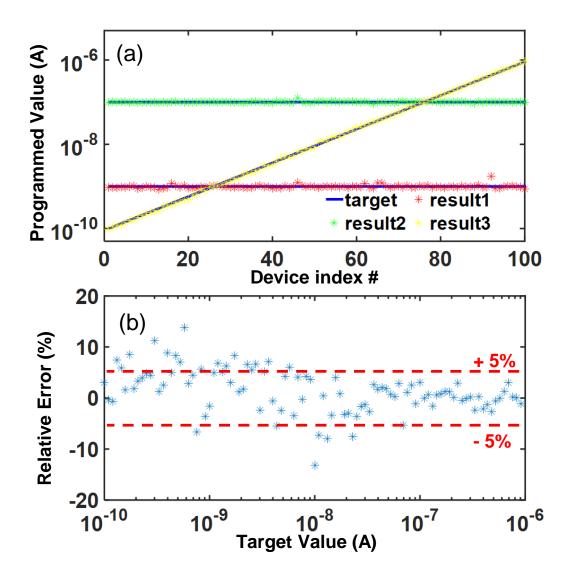

Fig. 22. (a) Measured versus target weights for 100 devices, and (b) Measured tuning error for 100 devices at a tuning precision target of 5%.

Fig. 22 illustrates the analog tuning capability of the array. All 10×10 array cells have been tuned one-by-one by an automatic feedback controlled application of alternating programming pulses to their source electrodes and erasing pulses to their erase gates. After each tuning pulse, the external control circuitry read out the cell output current at standard bias conditions, and made a decision about the next pulse's destination and amplitude, until the read-out current has reached the target value with the 5% precision [68]. Fig. 22a shows the results of 3 separate experiments of tuning all 100 cells of the array to different target

values of the output current: 1 nA (red line), 100 nA (green line), and an exponential function of the cell number, within the rage from 100 pA to 1  $\mu$ A (yellow line). Fig. 22b shows the relative errors achieved in last experiment. The data mean that larger tuning errors (of the order of 10%) take place for smaller target currents, because of the relative large intrinsic noise of the devices.

## **IV. Vector Matrix Multiplication**

The essence of the advantages using nonvolatile memory for neuromorphic network is the fact that in analog circuits, the vector-by-matrix multiplication, i.e. the key operation performed at signal propagation through any neuromorphic network, is implemented on the physical level, in a resistive crossbar circuit, using the fundamental Ohm and Kirchhoff laws (Fig. 23). On the other hand, the basic handicap of analog circuits, their finite precision, is not crucial in neuromorphic networks, due to the inherently high tolerance of their operation to synaptic weight variations [27].

Fig. 23. Analog vector-by-matrix multiplication in a crossbar with adjustable crosspoint devices. For clarity, the output signal is shown for just one column of the array.

## A. Based on 180-nm ESF1 Floating-Gate Array

We redesigned and optimized the ESF1 Flash memory from Silicon Storage Technology, Inc. (SST) (See Fig. 6) to build an analog vector-by-matrix multiplier in 180-nm technology for deep learning friendly hardware implementations. Because the original Flash memory from SST was optimized for digital memory applications, we reconfigured the original

memory array to enable precise tuning of individual cell inside the array for analog computing purposes [61].

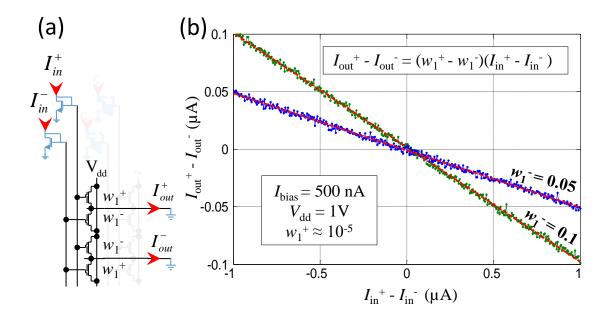

As a first step, we have used the high-precision tuning in the modified array for a preliminary demonstration of a small-scale four-quadrant gate-coupled vector-by-matrix multiplication [66], in which peripheral floating-gate transistors had been implemented with the same SST memory technology and integrated on the same chip shown in Fig. 17.

To implement the vector-by-matrix multiplication, we have used the gate coupling of the tunable floating gate cells of each column of the array with a similar "peripheral" cell, with the virtual-bias condition imposed (by external circuitry) on the output (row) wires [18] (Fig. 24a). Since all the cells sharing the same gate have the same gate voltage, in the subthreshold operation mode the component  $w_i$  of the output  $I_{out}$  is proportional to the input  $I_{in}$ :

$$\begin{split} I_{in} &= I_0 \exp \left\{ q \frac{V_g - V_{\text{th}}^{(p)}}{n k_{\text{B}} T} \right\}, \\ I_{out} &= I_0 \exp \left\{ q \frac{V_g - V_{\text{th}}^{(i)}}{n k_{\text{B}} T} \right\} \equiv w_i I_{in} \end{split} \tag{3}$$

with current-independent proportionality coefficients  $w_i$ , which are determined by the differences of threshold voltages  $V_{th}$  of the array cells and the peripheral transistors:

$$w_{i} = \exp\left\{q \frac{V_{\text{th}}^{(p)} - V_{\text{th}}^{(i)}}{nk_{\text{B}}T}\right\}$$

(4)

In turn, each threshold voltage is determined by the analog state (physically, the floating gate charge) of the cell, so that each  $w_i$  may be adjusted to the desirable value.

The results (Fig. 24) show an excellent linearity (derivate variation below 1%) of circuit's transfer characteristics over a wide range of input currents. In the meanwhile, we achieved an area of ~50F<sup>2</sup> for multiply-and-accumulate (MAC) unit.

Fig. 24. Preliminary experimental results for a gate-coupled vector-by-matrix multiplier: (a) circuit schematics and (b) measured transfer characteristics for two sets of "weights" (matrix elements)  $w_1$ . Dotted lines show another column of the array, disengaged in these experiments.

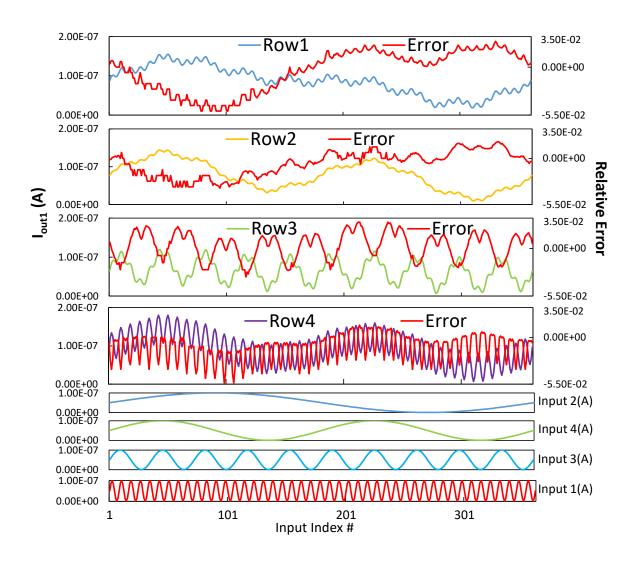

As a simple illustration of multiplier's operation, we also fabricated and tested a  $4 \times 4$  analog vector-by-matrix multiplier (See Fig. 25) to better evaluate the performance of nonvolatile memory approach. Fig. 26 shows the results of multiplication of 4 input signals by 16 different weights:  $\{w_{11}, w_{12}, \dots, w_{44}\} = \{0.1875, 0.5, 0.125, 1; 0.125, 0.9375, 0.0625, 0.4375, 0.875, 0.125, 0.375, 0.125, 0.0625, 0.6875, 0.8125, 0.25\}$ , performed by 4 columns and 4 rows of the array, tuned with a 1% precision. We also investigated the sensitivity of multiplier precision on a selected range of array and peripheral weights, current range, and find optimal operating conditions with presence of mismatch, variations, weight-dependent subthreshold conductance slope, capacitive cross-talk, noise, retention and tuning precision.

With all factors mentioned above, we evaluate our fabricated  $4 \times 4$  analog vector-by-matrix multiplier to achieve a total precision of ~5%.

Fig. 25. Fabricated  $4 \times 4$  analog vector-by-matrix multiplier based on 180-nm ESF1 NOR flash memory and high voltage pass-gate integrated on chip.

Fig. 26. Real outputs at a 4-input vector-by-vector multiplication, and their difference (red lines). The four inputs are quasi-DC currents sampled from sine function 50 nA ×  $[1+Sin(2\pi \times Input Index\# \times f)]$ , with f=1/8, 1/36, 1/180, and 1/360.

## B. Based on 55-nm ESF3 Floating-Gate Array

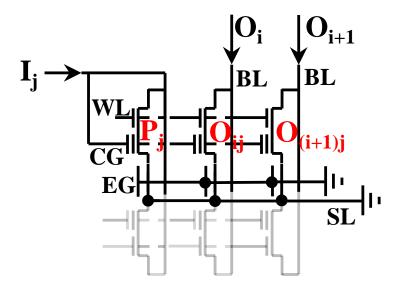

Similar to 180-nm ESF1 technology, to implement the vector-by-matrix multiplication, we have used the gate coupling of the tunable floating gate cells of each row of the array with a similar "peripheral" cell, with the virtual-bias condition imposed (by external circuitry) on the output (column) wires (Fig. 27).

Fig. 27. The vector-by-matrix multiplication scheme based on gate coupling of the floating-gate cells. (For clarity, only one peripheral (P) and two array (O) cells of the same  $(j^{th})$  row are shown.

Since all cells of the same row share the same coupling gate voltage  $V_j$ , in the subthreshold operation mode the j-th component  $O_{ij}$  of the output current  $O_i$  in the i-th column is proportional to the input current  $I_j$  in the j-th-row:

$$\begin{split} I_{j} &= I_{0} \exp \left\{ q \frac{V_{j} - V_{\text{th}}^{(j)}}{n k_{\text{B}} T} \right\}, \\ O_{i} &= \sum_{j} O_{ij} = \sum_{j} I_{0} \exp \left\{ q \frac{V_{j} - V_{\text{th}}^{(i,j)}}{n k_{\text{B}} T} \right\} \equiv \sum_{j} w_{ij} I_{j}, \end{split} \tag{5}$$

with current-independent proportionality coefficients  $w_{ij}$ , which are determined by the differences of threshold voltages  $V_{th}$  of the array cells and the peripheral transistors:

$$w_{ij} = \exp\left\{q \frac{V_{\text{th}}^{(j)} - V_{\text{th}}^{(i,j)}}{nk_{\text{B}}T}\right\}$$

(6)

In turn, each threshold voltage is determined by the analog state (physically, the floating gate charge) of the cell, so that each  $w_{ij}$  may be adjusted to the desirable value (typically, below 1).

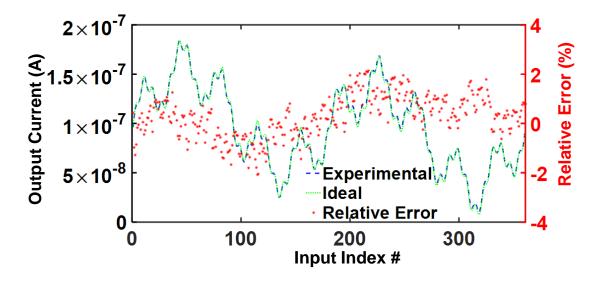

As a simple illustration of multiplier's operation, Fig. 28 shows the results of multiplication of 4 input signals by 4 different weights:  $w_1 = 0.25$ ,  $w_2 = 1$ ,  $w_3 = 0.5$ , and  $w_4 = 0.125$ , performed by 4 cells of one column of the array, tuned with a 1% precision. This experiment demonstrates that the relative error, incorporating contributions from all sources (device noise, state retention, impedance mismatch, parameter variation, tuning precision, and capacitive crosstalk) does not exceed 2%.

Fig. 28. Ideal (green line) and real (blue dashes) outputs at a 4-input vector-by-vector multiplication, and their difference (red dots). The four inputs are quasi-DC currents sampled from sine function 50 nA  $\times$  [1+ Sin(2 $\pi$   $\times$  Input Index#  $\times$  f)], with f = 1/8, 1/36, 1/180, and 1/360.

According to Eq. (6), in the coupled-gate operation mode, much of the thermal dependence of the subthreshold current is compensated, but besides the special case  $w_{ij} = 1$ , the compensation is incomplete. Indeed, our measurements have confirmed that in

agreement with this relation, that as temperature is raised from 25°C to 85°C, weight  $w_{ij}$ , initially equal to 0.9, increases by ~10%.

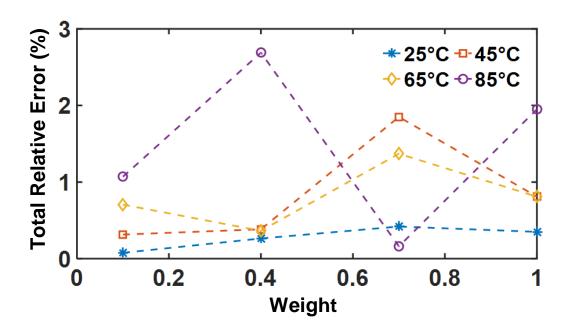

However, there is a straightforward way to decrease the temperature sensitivity, at the cost of a two-fold increase of hardware. For that, one can subtract output currents of two cells (say, those shown in Fig. 27), with their individual weights tuned to, respectively, ( $w_b + w/2$ ) and ( $w_b - w/2$ ). Here w is the desired net weight, and  $w_b$  is the "bias weight", which may be optimized to suppress the temperature dependence of the new output current. A straightforward analysis of this scheme, using Eq. (6), shows that after such optimization, the temperature drift of the output may be reduced to less than 1% at the [25°C, 85°C] interval, for any weight  $0 < w_{ij} < 1$ . Fig. 29 shows the results of our preliminary experiments with this mode, showing the drifts not exceeding 2.7% in that temperature interval.

Fig. 29. The total relative error of the reproduction of a 100 nA input signal for several values of w, at various temperatures.

# V. Mixed-Signal Neurocomputing Systems

### A. Fabricated Pattern Classifier based on NOR Flash Array

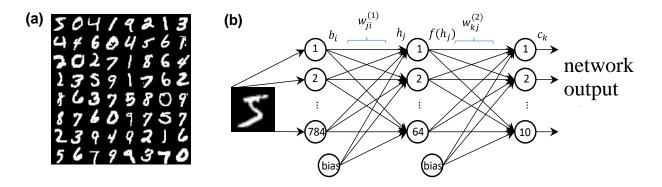

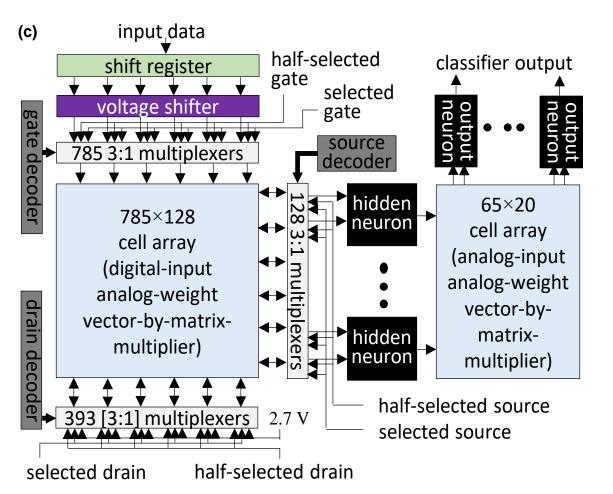

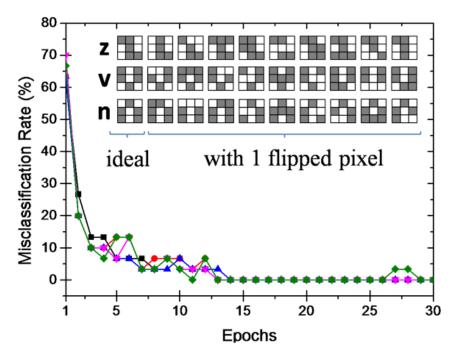

Here we report a prototype 28×28-binary-input, 10-output, 3-layer neuromorphic network based on arrays of highly optimized embedded nonvolatile floating-gate cells, redesigned from a commercial 180-nm NOR flash memory. The implemented network could perform a high-fidelity classification of patterns of the standard MNIST benchmark with record-breaking speed and energy efficiency.

#### 1. Network Deisgn

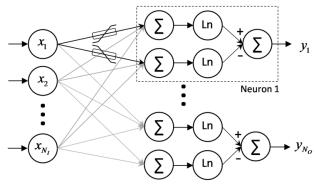

The implemented neuromorphic network (Fig. 30) is a 3-layer (one-hidden-layer) perceptron with 784 binary inputs  $b_i$ , which may represent, for example, 28×28 black-and-white pixels of an input image (such as the MNIST dataset images shown in Fig. 30a), 64 hidden layer neurons with the rectified-tanh activation function, and 10 output neurons (Fig. 30b). The goal of the network is to perform the pattern inference by the following sequential transformation of the input signals:

$$h_{j} = \sum_{i=1}^{784} w_{ji}^{(1)} b_{i} + w_{j,785}^{(1)}, \quad c_{k} = \sum_{j=1}^{64} w_{kj}^{(2)} f(h_{j}) + w_{k,65}^{(2)} f_{\text{max}},$$

$$f(h) \equiv f_{\text{max}} \times \begin{cases} \tanh(h), & \text{for } h \ge 0, \\ 0, & \text{for } h < 0. \end{cases}$$

(7)

Here  $h_j$  and  $f_j$  (with  $j = 1, 2, \dots, 64$ ) are, respectively, the input and output signals of the hidden-layer neurons,  $c_k$  (with  $k = 1, 2, \dots, 10$ ) are the output signals, providing the class of the input pattern, while  $w^{(1)}$  and  $w^{(2)}$  are two matrices of tunable synaptic weights,

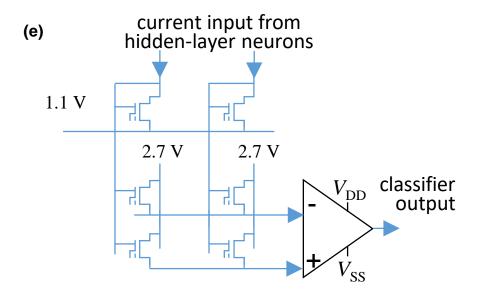

Fig. 30. Network architecture: (a) Typical examples of B/W hand-written digits of the MNIST benchmark set. (b) Graph representation of our 3-layer perceptron network. Each synapse is implemented using a differential pair of floating-gate memory cells. (c) High-level architecture, with the weight tuning circuitry for the second array (like that of the first one) not shown for clarity. (d) A 2×2-cell fragment of the first crossbar array shown together with a hidden-layer neuron, consisting of a differential summing operational amplifier pair and an activation-function circuit. (e) A 2×2-cell fragment of the second crossbar array with an output-layer neuron; these neurons do not implement an activation function. The voltage shifter, shown on panel (c), enables using voltage inputs of both polarities over a 1.65V bias, and is also used to initiate the classification process by increasing the input background from 1.8 V to 4.2 V.

characterizing the coupling of the adjacent network layers. In our network, these weights are provided by floating-gate cells of two crossbar arrays of the floating-gate memory cells providing tunable weights (Fig. 30c). Each neuron also gets an additional input from a bias

node, with a tunable weight based on a similar cell (Fig. 30b). With the differential-pair implementation of each synapse (see below), the total number of utilized floating-gate memory cells is  $2\times[(28\times28+1)\times64+(64+1)\times10]=101,780$ .

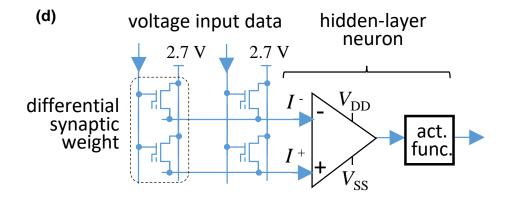

The mixed-signal vector-by-matrix multiplication in the first crossbar array is implemented by applying input voltages (4.2 V for black pixels or 0 V for white ones) directly to the gates of the array cell transistors, with fixed voltages on their sources (1.65 V) and drains (2.7 V) – see Fig. 30d. As a result, the transistor source-to-drain current of the cell located at the crosspoint of the  $i^{th}$  column and the  $j^{th}$  row of the array does not depend on the state of any other cells, and is equal to the product of the binary input voltage  $b_i$  by the analog weight  $w_{ji}$  (1) pre-recorded in the memory cell. The sources of the transistors of each row are connected to a single wire (with an externally-fixed voltage on it), so that the  $j^{th}$  output current of the array is just the sum of products  $w_{ji}$  (1) $b_i$  over all columns i, thus implementing the vector-by-matrix multiplication described by the first of Eqs. (7).

Actually, in order to reduce the random drifts, and also to work with zero-centered signals  $h_j$ , we are using a differential scheme, in which each synaptic weight is recorded in two adjacent cells of each column, and the output currents (in Fig. 30d,  $I_j^+$  and  $I_j^-$ ) of two adjacent cell rows are subtracted in an operational amplifier, with its output,  $h_j \propto I_j^+ - I_j^-$ , passed to the activation function circuit performing the function f(h). The accepted sharing of the weight  $w_{ji}^{(1)}$  between the two cells of the differential pair is very simple: one of the cells (depending of the sign of the desirable weight) is completely turned off, giving virtually no contribution to the output current. This arrangement keeps half of the cells virtually idle, but simplifies the design and speeds up the weight tuning process.

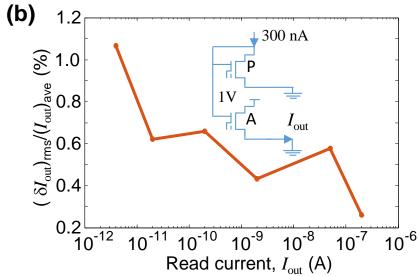

The analog vector-by-matrix calculation in the second array is performed using the gatecoupled approach (Fig. 30e). In this approach [66], the synaptic gate array is complemented by the additional row of "peripheral" cells, which are physically similar to the array cells, and hence sharing the same subthreshold slope  $\beta$ . The gate electrode of the peripheral cell of each column is connected to those of all cells of this column, so that their voltages  $V_{GS}$  are also equal. Applying Eq. (1) to the current of the cell located at the crosspoint of the  $k^{th}$  row and the  $j^{th}$  column of the array ( $I_{kj}$ ), and that of the peripheral cell of this column ( $I_j$ ), and dividing the results, we get

$$w_{kj}^{(2)} \equiv \frac{I_{kj}}{I_j} = \exp\left\{\beta \frac{\left(V_t\right)_j - \left(V_t\right)_{kj}}{V_T}\right\}$$

(8)

The resulting currents  $I_{kj}$  are summed up exactly as those in the first array (actually, with the similar differential scheme for drift reduction), so that if the array is fed by the output currents of the activation function circuits,  $I_j \propto f(h_j)$ , it performs the second vector-by-matrix multiplication described by Eq. (7), with the synaptic weights given by Eq. (8), which depend on the preset memory states of the corresponding cells, but are independent of the input currents. To minimize the error due to the dependence of  $\beta$  on the memory state (see the inset in Fig. 4), in the second array we used a higher gate voltage range (1.1 V to 2.7 V), with the upper bound due to the technology restrictions.

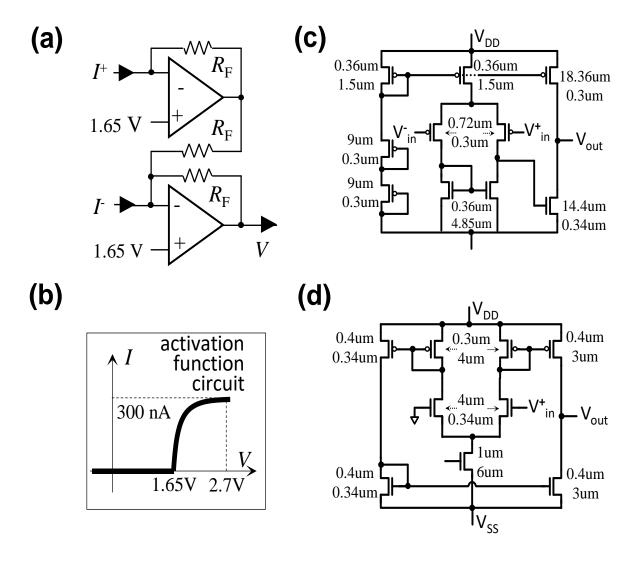

Fig. 31a shows the circuit used to subtract the currents  $I^+$  and  $I^-$  of the differential-scheme rows, based on two operational amplifiers (Fig. 31c). Assuming that the resistances  $R_F$  are equal, that the outputs of both opamps do not saturate (which is ensured by the following relation between of the chosen value  $R_F = 16 \text{ K}\Omega$  in the first layer and  $R_F = 128 \text{ K}\Omega$  in the second one, and the maximum value of currents  $I^{\pm}$ :  $I_{\text{max}}R_F < 1 \text{ V}$ ) the output voltage of the scheme is

$$V = R_{\rm F} \left( I^+ - I^- \right) + const \tag{9}$$

Fig. 31b shows the rectified-tanh activation function f(h) used in the hidden-layer neurons (see Eq. (5) of the main text), with  $h[V] = 10R_F[\Omega] (I^+ - I^-) [A]$  and  $f_{max} = 300$  nA, while Fig. 31d shows the circuit used for the implementation of this function.

Fig. 31. (a) Circuit-level diagram of a differential summing amplifier used in the hidden-layer and output-layer neurons;  $RF_1 = 16 \text{ K}\Omega$  for hidden neurons, and  $RF_2 = 128 \text{ K}\Omega$  for output neurons. (b) Implemented activation function. (c, d) Transistor-level schematics of: (c) the operational amplifier and (d) the activation function;  $V_{SS} = 0 \text{ V}$ ,  $V_{DD} = 2.7 \text{ V}$ .

The desirable synaptic weights, calculated in an external computer implementing a similar "precursor" network, using the standard error backpropagation algorithm, were imported into the network by analog tuning of the memory state of each floating-gate cell using peripheral analog demultiplexer circuitry (Fig. 30c). In order to simplify this first, prototype design, the weights were tuned one-by-one, by applying proper bias voltage sequences to selected and half-selected lines [60]. (In principle, this process may be significantly parallelized.) The large voltages required for the weight import are decoupled from the basic, low-voltage circuitry, using high-voltage pass transistors. The input pattern bits are shifted serially into a 785-bit register before each classification; to start it, the bits are read out into the network in parallel.

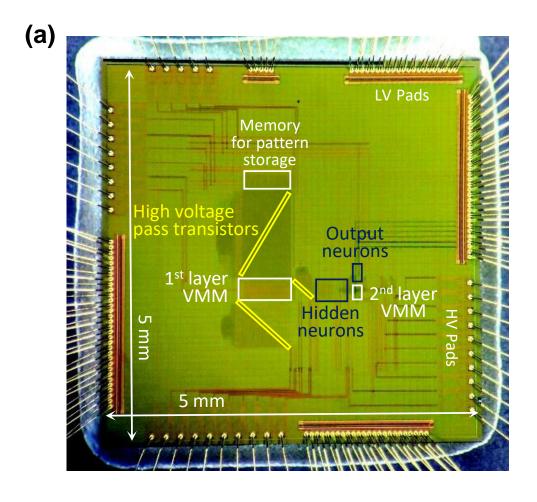

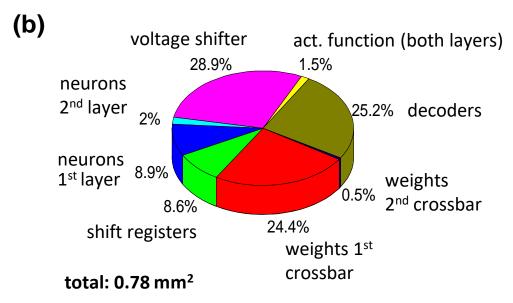

The digital encoders and shift register circuits and their layouts were synthesized from Verilog in a standard 1.8 V digital CMOS process. All other circuits were designed manually for the embedded 180-nm process of SST Inc.. (Such a design was practicable due to the modular, repetitive design of the circuit.) All active components of the circuit have a total area of 0.78 mm<sup>2</sup> (Fig. 32), with the two synaptic arrays occupying less than a quarter of this area, while the total chip area, including very sparse routing (which was not yet optimized for this design), is about 5×5 mm<sup>2</sup>.

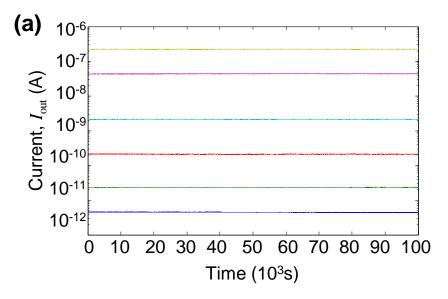

#### 2. Network Testing

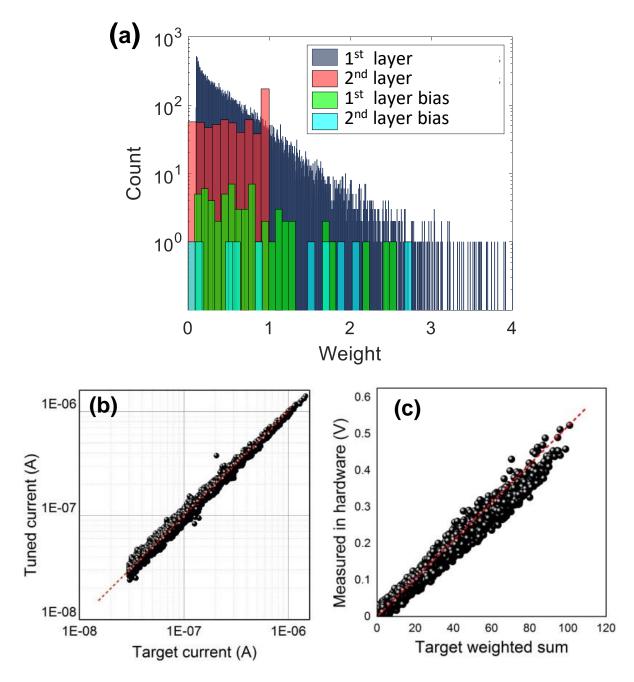

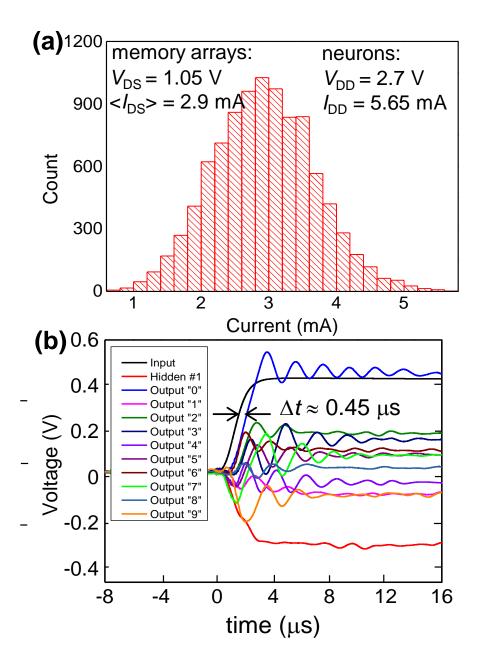

Because of the digital (fixed-voltage) input of the first synaptic array, the subthreshold conduction was not enforced there, so that the output currents of some cells exceeded 300 nA (Figs. 33a, b). To reduce the computation error due to the potential slope mismatch between peripheral and array cells, all peripheral floating gate transistors in the second array were tuned to provide output currents of 300 nA at  $V_G = 2.7$  V, i.e. at the largest voltage that

Fig. 32. (a) A micrograph of the chip, and (b) an area breakdown of its active components (excluding wiring between the blocks, which was not optimized at this stage).

Fig. 33. Weight export statistics: (a) A histogram showing the imported cell current values (weights), measured at  $V_D = 2.7$  V, and  $V_S = 1.65$  V and  $V_G = 4.2$  V in the first synaptic array, and  $V_S = 1.1$  V and  $V_G = 2.7$  V for the second one, which were used in the experiment. (b) Comparison between the target synaptic cell currents (computed at the external network training) and the actual cell currents measured after their import, i.e. cell tuning. (c) The similar comparison for the positive fraction of hidden neuron output, computed for all test patterns. (The negative outputs are not shown, because they are discarded by the used activation function.) Red dashed lines are guides for the eye, corresponding to the perfect weight import.

can be supplied by the hidden layer neuron in our design. With such scheme, the error is conveniently smallest for the largest weight  $w_{ki} = 1$ , corresponding to the array cell tuned to run a current 300 nA at  $V_{GS} = 1.6$  V. The target current values for all cells in the second array (excluding bias ones) were ensured to be between 0 and 300 nA by clipping the weights during training of the precursor network.

To decrease the weight import time, only one cell of each pair, corresponding to a particular sign of the weight value, was tuned, while its counterpart was kept at a very small, virtually zero, and initial conductance. Additionally, all non-bias cells in the first array, for which the target conductances were below 30 nA, were also not tuned, because of their negligible impact on the classification fidelity, confirmed by modeling. As a result, only about ~30% of the cells were actually fine-tuned. Because of the sequential character of the tuning process, it took several hours to complete it, with the chosen accuracy, for the whole chip. (In future, the tuning may be greatly sped up by adjusting multiple weights at a time via integrated on-chip tuning circuitry [58], and using better tuning algorithms we have developed [61].)

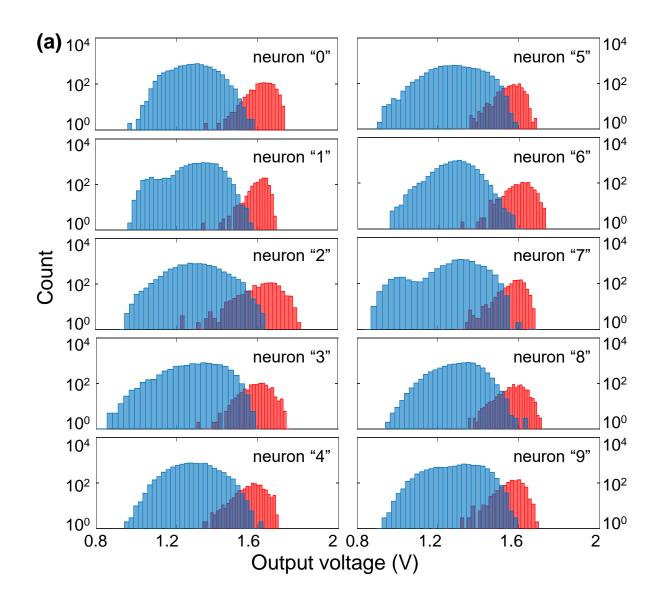

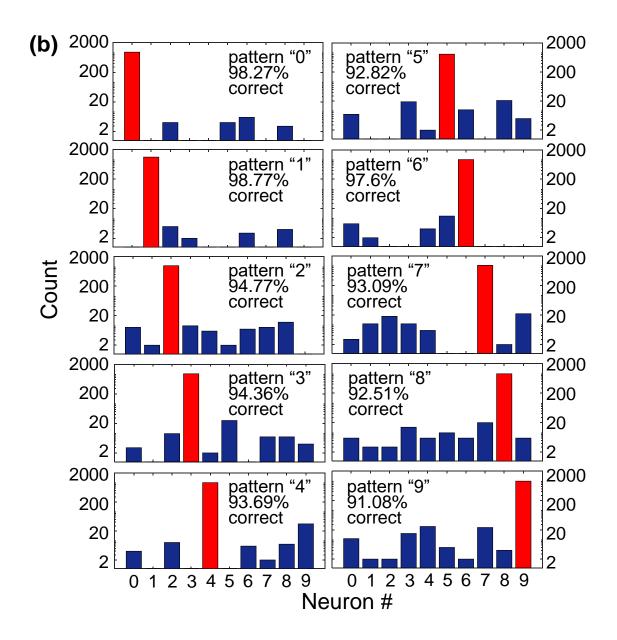

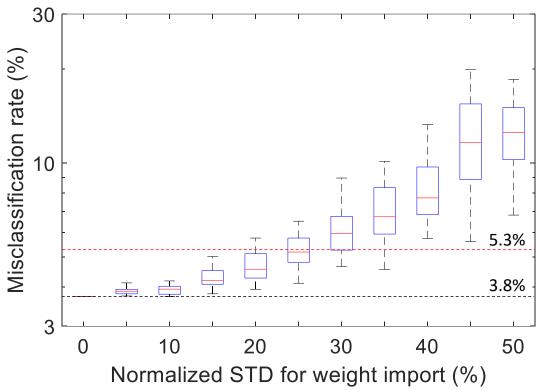

Moreover, also to speed up the import process, the weigh import accuracy for a single cell tuning was set to relatively high value of 5%. As Fig. 33b indicates, some of the already tuned cells were disturbed beyond the target accuracy during the subsequent weight import. In this first experiment, these cells were not re-tuned, in part because even for such rather crude weight import the experimentally tested classification fidelity (94.65%) on MNIST benchmark test patterns (Fig. 34) is already remarkably close to the simulated value (96.2%) for the same network (Fig. 35). Both these numbers are also not too far from the maximum fidelity (97.7%) of the similar perceptron of this size, optimized without hardware constrains.

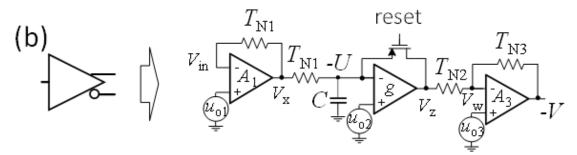

Fig. 34. Experimental results for the classification of all 10,000 MNIST test set patterns: (a) Histograms of voltages measured on each output neuron. Red bars correspond to the patterns whose class belongs to this particular output, while the blue ones are for all remaining patterns. (b) Histograms of the largest output voltages (among all output neurons) for all test patterns of each class, showing that the correct outputs (red bars) always dominate. Note the logarithmic vertical scales.