#### UNIVERSITY OF CALIFORNIA

Santa Barbara

# Data Learning Methodologies for Improving the Efficiency of Constrained Random Verification

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Wen Chen

Committee in charge:

Professor Li-C. Wang, Chair

Professor Forrest Brewer

Professor Malgorzata Marek-Sadowska

Dr. Jayanta Bhadra

September 2014

| The dissertation of Wen Chen is approved. |

|-------------------------------------------|

|                                           |

|                                           |

| Professor Forrest Brewer                  |

| Professor Forrest Brewer                  |

|                                           |

| Professor Malgorzata Marek-Sadowska       |

|                                           |

| Dr. Jayanta Bhadra                        |

|                                           |

| Professor Li-C. Wang, Committee Chair     |

### Data Learning Methodologies for Improving the Efficiency of Constrained Random Verification

Copyright © 2014

Wen Chen

Dedicated to my mom and dad

## Acknowledgements

First of all, I express my deepest appreciation and gratitude to my advisor Professor Li-C. Wang for his continuous guidance and tremendous patience through the past four years. Not only did he teach me how to conduct solid research, but he also guided me to becoming a more mature person in life. The mindset and philosophy I developed while working with Li will be definitely beneficial for a lifetime.

I would like to thank my colleagues in Freescale Semiconductor Inc. for their help during my research internships there. I owe special thanks to Dr. Jay Bhadra, my manager and PhD committee member, for his mentorship and enormous help with my research and internships. I am also thankful to Dr. Magdy Abadir and Dr. Shaun Feng for their mentorship and support for my projects. Also, I would like to thank Sanjay Gupta, Robert Page, Daniel Pinero, Prashant Bansal and Larry McConville for their technical help with setting the verification environment.

I would like to thank the faculty at the University of California, Santa Barbara. Specially, I am grateful to the members of my PhD committee, Professor Forrest Brewer and Professor Margaret Marek-Sadowska, for their guidance and valuable feedback.

I feel very fortunate to meet my adorable labmates in Li's group. Particularly, I would like to acknowledge Po-Hsieh Chang and Nik Sumikawa for their help when I started as a junior graduate student. I would like to thank Jeff Tikkanen, Gagi Drmanic, Vinayak Kamath, Sebastian Siatkowski, Kuo-Kai Hsieh and Chia-Ling Chang for discussions and collaborations.

I really appreciate the love and support from all my friends. I would like to thank Yang Li, Yang Lin, Liming Chen and many other friends here at UCSB for their company and comfort during the past four years. I also owe thanks to Gang Li, Qiang Xu, Tao Mao, Cheng Zhuo, Jia Zeng and many other friends who are not here, for their spiritual support for my PhD endeavor.

Last but certainly not the least, I dedicate this dissertation to my parents, with my gratitude for their unconditional support and care in my lifetime.

## Curriculum Vitae

#### Wen Chen

#### **EDUCATION**

| 2010 - 2014 | PhD in Electrical and Computer Engineering, |

|-------------|---------------------------------------------|

|             | University of California, Santa Barbara.    |

| 2008 - 2010 | M.S. in Computer Science and Engineering,   |

|             | University of Michigan, Ann Arbor.          |

| 2004 - 2008 | B.S. in Electrical Engineering,             |

|             | Zhejiang University, Hangzhou, China.       |

#### **PUBLICATIONS**

- Wen Chen, Li-C. Wang, Jay Bhadra, Madgy S. Abadir, Simulation Knowledge Extraction and Reuse in Constrained Random Verification, ACM/IEEE Design Automation Conference (DAC), June 2013

- Wen Chen, Li-C. Wang, Jay Bhadra, Madgy S. Abadir, Novel Test Analysis to Improve Structural Coverage A Commercial Experiment, in Proc. IEEE/ACM International Symposium on VLSI Design, Automation and Test (VLSI-DAT), April 2013

- 3. Vinayak Kamath, Wen Chen, Nik Sumikawa, Li-C. Wang, Functional test content optimization for peak-power validation An experimental study, IEEE International Test Conference (ITC), Nov 2012

- Wen Chen, Nik Sumikawa, Li-C. Wang, Jayanta Bhadra, Xiushan Feng, Magdy S. Abadir, Novel test detection to improve simulation efficiency

A commercial experiment, IEEE/ACM International Conference on Computer Aided Design (ICCAD), Nov 2012

#### FIELD OF STUDY

Electrical and Computer Engineering

Professor Li-C. Wang

#### Abstract

#### Data Learning Methodologies for Improving the Efficiency of Constrained Random Verification

by Wen Chen

Functional verification continues to be one of the most time-consuming steps in the chip design cycle. Simulation-based verification is well practised in industry thanks to its flexibility and scalability. The completeness of the verification is measured by coverage metrics. Generating effective tests to achieve a satisfactory coverage level is a difficult task in verification. Constrained random verification is commonly used to alleviate the manual efforts for producing direct tests. However, there are yet many situations where unnecessary verification efforts in terms of simulation cycles and man hours are spent. Also, it is observed that lots of data generated in existing constrained random verification process are barely analysed, and then discarded after simplistic correctness checking. Based on our previous research on data mining and exposure to the industrial verification process, we identify that there are opportunities in extracting knowledge from the constrained random verification data and use it to improve the verification efficiency.

In constrained random verification, when a simulation run of tests instantiated by a test template cannot reach the coverage goal, there are two possible reasons: insufficient simulation, and improper constraints and/or biases. There are three actions that a verification engineer can usually do to address the problem: to simulate more tests, to refine the test template, or to change to a new test template. Accordingly, we propose three data learning methodologies to help the engineers make more informed decisions in these three application scenarios and thus improve the verification efficiency.

The first methodology identifies important ("novel") tests before simulation based on what have been already simulated. By only simulating those novel tests and filtering out redundant tests, tremendous resources such as simulation cycles and licenses can be saved. The second methodology extracts the unique properties from those novel tests identified in simulation and uses them to refine the test template. By leveraging the extracted knowledge, more tests similar to the novel ones are generated. And thus the new tests are more likely to activate coverage events that are otherwise difficult to hit by extensive simulation. The third methodology analyses a collection of existing test items (test templates) and identifies feasible augmentation to the test plan. By automatically adding new test items based on the data analysis, it alleviates the manual efforts for closing coverage holes.

The proposed data learning methodologies were developed and applied in the setting of verifying commercial microprocessor and SoC platform designs. The experiments in this dissertation were conducted in the verification environment of a commercial microprocessor and a SoC platform in Freescale Semiconductor Inc. and were in parallel with the on-going verification efforts. The experiment results demonstrate the feasibility and effectiveness of building learning frameworks to improve verification efficiency.

## Contents

| C  | urric | ulum Vitae                                              | VII                    |

|----|-------|---------------------------------------------------------|------------------------|

| A  | bstra | ıct                                                     | ix                     |

| Li | st of | Figures                                                 | $\mathbf{x}\mathbf{v}$ |

| Li | st of | Tables                                                  | viii                   |

|    |       |                                                         |                        |

| 1  | Inti  | roduction                                               | 1                      |

|    | 1.1   | Background                                              | 1                      |

|    | 1.2   | Motivation                                              | 2                      |

|    | 1.3   | The Proposed Methodologies                              | 5                      |

|    | 1.4   | Dissertation Organization                               | 7                      |

| 2  | Bac   | ekground and Related Works                              | 8                      |

|    | 2.1   | Simulation-based Verification                           | 8                      |

|    | 2.2   | Verification Test Generation                            | 9                      |

| 3  | Ker   | enel-Based Novelty Detection for Simulation Cost Reduc- |                        |

|    | tion  | 1                                                       | <b>12</b>              |

|    | 3.1   | Overview                                                | 12                     |

|    | 3.2   | Introduction                                            | 13                     |

|    | 3.3   | The Experimental Framework and Novel Tests              | 16                     |

|   |       | 3.3.1   | Existence of Novel Tests in Practice                | 17 |

|---|-------|---------|-----------------------------------------------------|----|

|   | 3.4   | The G   | raph-based Kernel Approach                          | 18 |

|   |       | 3.4.1   | Kernel Based Learning with SVM One-class            | 18 |

|   |       | 3.4.2   | The Coverage-independent Graph-based Kernel         | 20 |

|   |       | 3.4.3   | Model Building and Novelty detection                | 22 |

|   |       | 3.4.4   | Experiment Results                                  | 22 |

|   | 3.5   | Kernel  | Based on Estimated Coverage                         | 24 |

|   |       | 3.5.1   | Disadvantage of the Graph-kernel Approach           | 24 |

|   |       | 3.5.2   | Coverage-based Kernel                               | 24 |

|   |       | 3.5.3   | Estimating Coverage Before Simulation               | 26 |

|   |       | 3.5.4   | The Accuracy of Coverage Estimation                 | 27 |

|   |       | 3.5.5   | Dynamically Adjusting the Coverage Base Set $S$     | 28 |

|   |       | 3.5.6   | Results Compared to the Graph-based Kernel Method . | 30 |

|   |       | 3.5.7   | Result on Simulation of 10K Tests                   | 31 |

|   |       | 3.5.8   | Two Additional Results                              | 32 |

|   | 3.6   | Limita  | tion of the Single-Instruction Database             | 33 |

|   | 3.7   | Summa   | ary                                                 | 35 |

| 4 | Kno   | owledge | e Extraction Framework to Improve Functional Ver-   |    |

|   | ifica | tion C  | overage                                             | 36 |

|   | 4.1   | Overvi  | ew                                                  | 36 |

|   | 4.2   | Introdu | action                                              | 37 |

|   | 4.3   | Motiva  | tion and Related Works                              | 38 |

|   |       | 4.3.1   | The Benefits of Understanding Novel Tests           | 38 |

|   |       | 4.3.2   | What Knowledge to Extract                           | 40 |

|   |       | 4.3.3   | Related Works                                       | 42 |

|   | 4.4   | Featur  | e Generation                                        | 43 |

|   |       | 4.4.1   | Snippet-based Vector Representation                 | 43 |

|   |       | 4.4.2   | Defining a Set of Features at ISA level             | 45 |

|   |     | 4.4.3  | Feature Discretization                                     | 46 |

|---|-----|--------|------------------------------------------------------------|----|

|   | 4.5 | Know   | ledge Extraction by Rule Learning                          | 47 |

|   | 4.6 | Know   | ledge Reuse                                                | 50 |

|   |     | 4.6.1  | Rule Validation and Refinement                             | 50 |

|   |     | 4.6.2  | Rule Reuse                                                 | 50 |

|   | 4.7 | Learni | ing with Microarchitecture Features                        | 51 |

|   |     | 4.7.1  | Limitations of Learning at ISA Level                       | 51 |

|   |     | 4.7.2  | Hypothesis Pruning and Ranking                             | 53 |

|   |     | 4.7.3  | Adaptation of the Learning Methodology                     | 56 |

|   | 4.8 | Exper  | iment Results                                              | 58 |

|   |     | 4.8.1  | Experiment Environment                                     | 58 |

|   |     | 4.8.2  | The First Illustrative Result Based on Structural Coverage | 59 |

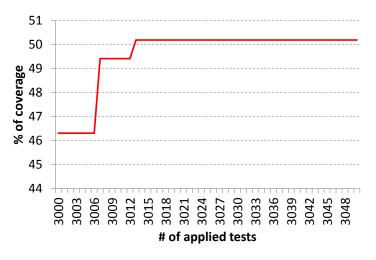

|   |     | 4.8.3  | The Second Result                                          | 62 |

|   |     | 4.8.4  | The Third Result                                           | 64 |

|   |     | 4.8.5  | The Fourth and Fifth Results                               | 66 |

|   | 4.9 | Summ   | ary                                                        | 68 |

| 5 | Dat | a Driv | en Test Plan Augmentation in Platform Verification         | 69 |

|   | 5.1 | Overv  | iew                                                        | 69 |

|   | 5.2 | Introd | uction                                                     | 70 |

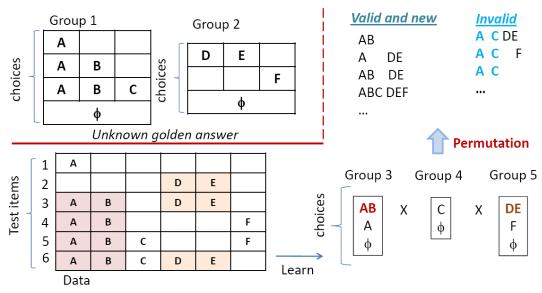

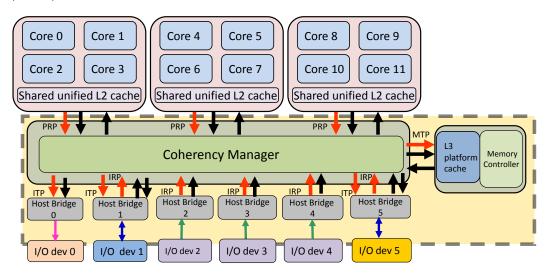

|   | 5.3 | Platfo | rm Verification                                            | 73 |

|   | 5.4 | Test F | Plan Augmentation Problem                                  | 77 |

|   | 5.5 | Platfo | rm Learning Algorithm                                      | 81 |

|   |     | 5.5.1  | Test Item Clustering                                       | 81 |

|   |     | 5.5.2  | Group Partitioning & Choice Generation                     | 82 |

|   |     | 5.5.3  | Further Group Merging                                      | 83 |

|   | 5.6 | Exper  | iment Results                                              | 84 |

|   | 5 7 | Summ   | arv                                                        | 87 |

#### Contents

| 6 Conclusions and Future Directions |     |                            |    |  |

|-------------------------------------|-----|----------------------------|----|--|

|                                     | 6.1 | Conclusions                | 88 |  |

|                                     | 6.2 | Future Research Directions | 90 |  |

## List of Figures

| 1.1  | When result is not satisfactory, there can be three ways to improve .        | 3  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | With non-redundant test identification and effective test template           |    |

|      | refinement, we are implementing a test template search process that          |    |

|      | can help us to find tests for hitting coverage holes $(k \ll N)$             | 6  |

| 3.1  | Illustration of novel test detection                                         | 14 |

| 3.2  | Three simulation runs to illustrate the existence of novel tests $$ .        | 17 |

| 3.3  | Illustration of kernel-based learning                                        | 20 |

| 3.4  | The framework of computing graph-based kernel                                | 21 |

| 3.5  | The framework of graph-based kernel                                          | 22 |

| 3.6  | Comparison of coverage curves with and without novelty detection             | 23 |

| 3.7  | Comparison of coverage curves with and without novelty detec-                |    |

|      | tion based on only the first 1800 tests in Figure 3.6 $ \dots  \dots  \dots$ | 24 |

| 3.8  | The framework of coverage-based kernel                                       | 25 |

| 3.9  | Illustration of coverage estimation flow                                     | 26 |

| 3.10 | Histogram of estimation accuracy of 2000 tests                               | 28 |

| 3.11 | An ideal iterative process with novel test detection                         | 29 |

| 3.12 | Comparison of coverage curves with and without novelty detec-                |    |

|      | tion using the coverage-based kernel; The same example shown                 |    |

|      | in Figure 3.6                                                                | 30 |

| 3.13 | Comparison of coverage curves with and without novelty detec-      |    |

|------|--------------------------------------------------------------------|----|

|      | tion using the coverage-based kernel; The same example shown       |    |

|      | in Figure 3.7                                                      | 30 |

| 3.14 | Comparison of coverage curves with and without novelty de-         |    |

|      | tection based on the middle plot example shown in Figure 3.2       |    |

|      | before                                                             | 31 |

| 3.15 | Results based on 2000 tests instantiated from 6 CFX instructions   | 32 |

| 3.16 | Results based on 200 hard-to-cover points in CFX                   | 33 |

| 3.17 | Comparison of coverage curves with and without novelty detec-      |    |

|      | tion using extended coverage-based kernel based on the third       |    |

|      | example plot shown in Figure 3.2                                   | 34 |

| 4.1  | Improving coverage by test template refinement                     | 39 |

| 4.2  | Histogram of covered events in LSU based on the frequency of       |    |

|      | being hit                                                          | 41 |

| 4.3  | Illustration of the learning goal                                  | 42 |

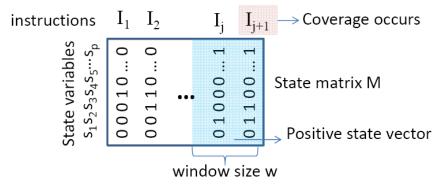

| 4.4  | Illustration of the slide window approach                          | 43 |

| 4.5  | Illustration of the transformed dataset                            | 44 |

| 4.6  | Illustration of a test program snippet                             | 46 |

| 4.7  | Illustration of a test template macro                              | 50 |

| 4.8  | Illustration of an example scenario in which rules cannot be       |    |

|      | efficiently learned by the approach discussed in previous sections | 52 |

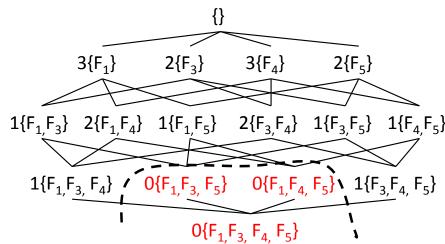

| 4.9  | Illustration of the concept lattice based on the example data set  | 55 |

| 4.10 | State matrix view of a test                                        | 56 |

| 4.11 | A positive state vector and its hypotheses                         | 56 |

| 4.12 | Toggle coverage on a block in LSU of the original simulation run   | 60 |

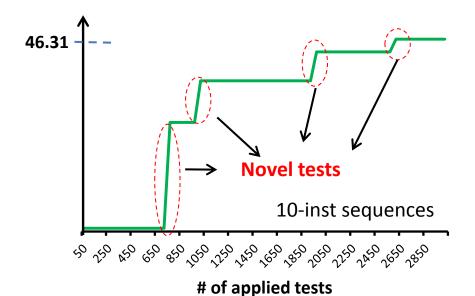

| 4.13 | Coverage improvement in the first iteration                        | 60 |

| 4.14 | Coverage improvement in the second iteration                       | 61 |

| 4.15 | Coverage improvement in the last iteration                         | 62 |

#### List of Figures

| 4.16 | Comparision between coverage w/ and w/o learning | 32 |

|------|--------------------------------------------------|----|

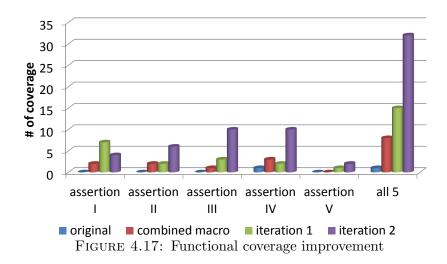

| 4.17 | Functional coverage improvement                  | 34 |

| 4.18 | 2 examples, coverage point sets A and B          | 36 |

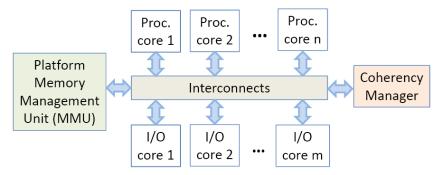

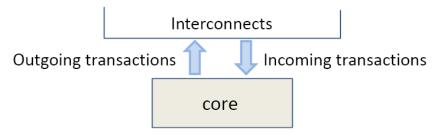

| 5.1  | Processor Verification vs Platform Verification  | 72 |

| 5.2  | Illustration of a platform                       | 73 |

| 5.3  | Transaction view in platform verification        | 74 |

| 5.4  | Illustration of platform verification            | 75 |

| 5.5  | Platform coverage examples                       | 76 |

| 5.6  | Illustration of the learning problem             | 79 |

| 5.7  | A simplified illustration of the SoC platform    | 35 |

## List of Tables

| 4.1 | Illustration of portion of a feature vector                  | 46 |

|-----|--------------------------------------------------------------|----|

| 4.2 | Example Data Set                                             | 54 |

| 4.3 | Comparison of event coverage between original 1000 tests and |    |

|     | 200 new tests                                                | 64 |

| 4.4 | Rules for macros $m_1$ and $m_2$                             | 65 |

| 4.5 | Coverage improvement after learning                          | 66 |

| 4.6 | Coverage improvement after learning                          | 67 |

| 5.1 | Result of test plan augmentation                             | 86 |

| 5.2 | Coverage gain of test plan augmentation                      | 86 |

## Chapter 1

## Introduction

#### 1.1 Background

Functional verification is acknowledged as a key bottleneck in the chip design cycle and industry has witnessed soaring sizes of verification teams [1]. The increasing sizes and complexities of emerging multi-core System-on-Chip (SoC) have placed greater challenges on verification [2][3][4]. Numerous efforts and resources have been dedicated to verifying the increasingly complicated microprocessors and the integration of heterogeneous cores at the SoC level. Hence, there is an enormous need for the development of advanced verification technologies.

Although the application of formal methods in verification has made remarkable advances, extensive simulation is still the most applicable for full-chip verification due to its scalability and flexibility. A typical verification flow includes a process of stimulus generation, simulation, result checking and coverage collection. One prevalent approach to simulation-based verification is

Constrained Random Verification (CRV), where the verification engineers encode constraints and biases as test templates and instantiate them into tests. The completeness of the verification is measured by coverage metrics. A satisfactory coverage level must be met before tape-out.

One difficult task in CRV is to generate effective tests to achieve high coverage. The quality of test generation usually improves along the verification process, as the verification engineers learn more in-depth knowledge about the design. However, this effort is conducted manually, usually in a trial-and-error manner. In the meanwhile, tons of data are generated in CRV, most of which are discarded during verification iterations. It would be helpful to analyse those data and extract useful information that can aid in improving the test generation. In recent years, the advances of data mining techniques have made it possible to analyse large volumes of data in various application fields [5]. This motivates us to investigate the feasibility and effectiveness of applying data mining techniques in functional verification. More specifically, we aim to develop learning-based methodologies to improve the efficiency of constrained random verification.

#### 1.2 Motivation

Suppose we were verifying a complex design with a constrained random verification framework. There was a particular coverage event we tried to hit. We developed a test template and let the framework to instantiate a number of tests and simulate them. After a long simulation run, we decided that it could not hit the event. We modified the test template and tried a new run. After a couple of trials, we still could not hit the event. At that point, we would

be hoping that there could be a tool that could guide us to more effectively produce a test template that could generate a test to hit the coverage event.

This is a typical scenario in constrained random verification. When we say that "my test template cannot hit the coverage hole," it can be actually due to two reasons:

Insufficient simulation How do we know that the test template is incapable of generating a test to hit the hole? Usually, we reach this conclusion by generating N tests. How do we know it will not hit the hole if we continue the simulation by generating  $100 \times N$  tests?

Improper input constraints and biases If we use a test template to produce 1M tests and still none of them can hit the hole, we probably would confidently conclude that we need to change the test template. Do we start from the scratch or do we start by modifying the existing input constraints and biases?

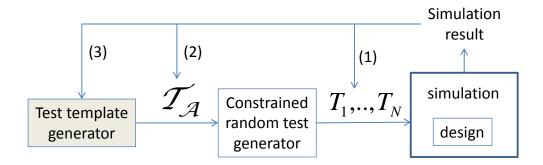

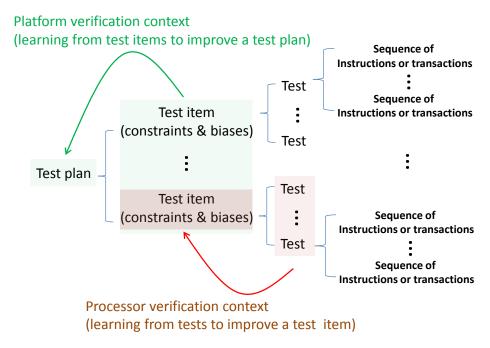

FIGURE 1.1: When result is not satisfactory, there can be three ways to improve

These two reasons imply three ways to improve the constrained random verification process when we encounter coverage holes. Figure 1.1 illustrates them. In the figure, we assume that a test template  $\mathcal{T}_{\mathcal{A}}$  is instantiated into N tests  $T_1, \ldots, T_N$ . Moreover, the test template is likely to be manually crafted by a verification engineer.

The first way to improve is to remove "redundancy" in  $T_1, \ldots, T_N$ .

For example, suppose we can afford (or decide) to simulate 2000 tests per test template. Currently, we simply instantiate 2000 tests and simulate them. Alternatively, we can instantiate 100K tests and identify the top 2000 novel ("non-redundant") tests. Intuitively, the alternative approach would be more effective.

The effectiveness can be viewed in two ways: (1) the 2000 novel tests achieve a higher coverage (or have a higher chance to hit the hole) than the original 2000 tests. (2) When we decide to stop using  $\mathcal{T}_{\mathcal{A}}$ , such a decision can be made with higher confidence.

The second way is to refine the test template  $\mathcal{T}_{\mathcal{A}}$ .

Refinement may mean to constrain and/or bias the template in such a way that the resulting tests have much higher probability for hitting a desired area (or a state) of the design. For example, a refinement increases the probability of satisfying some local conditions that we know would help to hit the hole.

The third way is to produce a new test template.

If we would like to have a tool that can automatically produce a test template for a desired target, in essence, this becomes solving the test generation problem. And we know that this would be a difficult problem. In practice, producing a new test template means someone writes the test template manually. However, when there is a collection of test templates, it is possible to

identify the insufficiency of the current collection and thus produce new test templates to augment the collection.

#### 1.3 The Proposed Methodologies

Accordingly, we developed three learning-based methodologies to help improve the efficiency in the three application scenarios mentioned above.

The first methodology is a novel test detection framework to reduce simulation cost. A novel test is dissimilar to those tests already simulated thus is likely to provide additional coverage. A kernel is defined to represent the similarity between two tests. By using the kernel-based novelty detection model, we can efficiently capture the covered space and filter out redundant tests. The idea of the novel test detection is not new, however, designing practical kernels is at the core of the novelty detection framework. We investigate the practical implementation of the kernel-based novel test detection framework and design a coverage-based kernel that is easy to implement.

The second methodology is a feature-based rule learning framework for extracting knowledge from novel tests. The novel tests embed valuable knowledge about how to activate special conditions in simulation. By analysing novel tests against a large population of non-novel tests based on a feature set, we can extract rules that explain the specialty of the novel tests. The learned rules can be used to refine the test templates and thus produce tests that are likely to hit the functional events that had low or zero coverage.

The first two methodologies are developed in the context of microprocessor verification. They can be used in combination to solve the problem of generating effective tests for a coverage goal. Even though we do not solve the test template generation problem directly, with these two components, novel test identification and test template refinement (based on learning from novel tests), we can build an iterative flow that implements a test template search process. Figure 1.2 illustrates this idea.

FIGURE 1.2: With non-redundant test identification and effective test template refinement, we are implementing a test template search process that can help us to find tests for hitting coverage holes  $(k \ll N)$

The third methodology is a test plan augmentation approach in the context of SoC platform verification. In platform verification, the constraints and biases are encoded as test items (like test templates in processor verification). By analysing a collection of test items, we can extract knowledge that captures the underlying verification intent and thus implies feasible augmentation to the test plan. By adding new test items based on this information, we can make the test plan more complete and thus ease the manual efforts for reaching coverage closure.

The first two methodologies have been applied on top of the verification environment of a high-performance low-power microprocessor within Freescale.

The third methodology has been applied in the verification of a commercial

SoC platform within Freescale. The experimental results prove the effectiveness and efficiency of the proposed methodologies and show promises of making practical tools based on them.

#### 1.4 Dissertation Organization

The rest of this dissertation is organized as follows: Chapter 2 provides necessary background information and reviews previous works for simulation-based verification and test generation. Chapter 3 reports the study of practical implementation of the novel test detection framework with the emphasis of kernel design. The feature-based rule learning framework is presented in Chapter 4, where the learned knowledge is used for test template refinement. The differences of processor verification and platform verification are discussed in Chapter 5, and a test plan augmentation approach for platform verification is presented. Chapter 6 concludes the dissertation and discusses future research opportunities to extend the materials addressed in this dissertation.

## Chapter 2

## Background and Related Works

#### 2.1 Simulation-based Verification

Simulation-based verification is the predominant methodology for full-chip verification in industry. Today's state-of-the-art verification flow includes a highly automated flow of test generation, simulation, correctness checking and coverage collection, with islands of manual labor [6]. The verification usually starts with the creation of a verification plan, which specifies the important functionalities and aspects of the design to verify. Then verification engineers prepare stimulus/tests via various approaches. The tests are simulated using RTL models and the correctness checking is done by comparing results with those produced by reference models or by checking with built-in checkers such as assertions. The completeness of the verification is measured by various coverage metrics [7]. There are two types of coverage metrics based on the way that they are defined: those that can be automatically extracted from the design code, such as toggle coverage, and those that are user-specified in order

to tie the verification environment to the design intent or functionality [8]. The former is referred to as structural coverage and the latter is referred to as functional coverage. Generating effective tests to achieve satisfactory coverage within bounded simulation cycles is crucial in meeting the verification budget requirement. In practice, a mixture of several test generation schemes are used, which we will discuss in Section 2.2

#### 2.2 Verification Test Generation

Direct tests are tests manually drafted by verification engineers for verifying specific scenarios. They are focus tests delicately designed for exercising particular mechanisms and thus are very effective in hitting the events of interest. However, the creation of direct tests requires a lot of manual efforts and indepth knowledge into the design. Thus, their primary use is to hit those corner cases that cannot be well exercised in extensive simulation. In addition, scenarios not considered by the designer might be overlooked by the test developers.

Random testing is an approach to overcome the costly manual labor and biases in direct tests. However, pure random testing proves ineffective due to two

reasons: (1) It generates a lot of invalid tests (2) It cannot target effectively

on the events of interest since the sampling space is enormous. Constrained

random verification [9] is a method that combines the verification knowledge

with the power of random test generation. Constraints are used to restrict

the test sampling space to ensure the tests are valid and focused on certain

verification subspace. The unconstrained aspects are randomized with certain

biases to increase the chances of hitting targets of interest while preserving the

potential of exposing bugs in scenarios overlooked by designers. As for microprocessor verification, a methodology called Random Test Program Generation (RTPG), originated in IBM, is designed to facilitate the constrained random verification for different processor models [10] [11]. In RTPG, a descriptive language is provided to describe the constraints and biases based on the architectural specifications and the test knowledge of the verification engineers [12]. The constraints and biases are encoded in test templates and are then fed to a test program generator. The generator converts the test generation problem into a Constraint Satisfaction Problem (CSP) and leverages CSP solvers to generate test programs satisfying the constraints [13].

Constrained random verification and direct tests are used as two prevalent approaches in industry. However, it might still be difficult to achieve a certain coverage level using both approaches. Coverage Directed Test Generation (CDTG) is a technique to generate stimulus to hit specific coverage targets. There are two approaches to CDTG: one is model-based and the other is learned-based or feedback-based [14].

In model-based CDTG, an abstract model such as Finite-State-Machine (FSM) of the design is built, and algorithms traversing the model are used to search for a path from the initial state/node to the state/node corresponding to the coverage point of interest. Commonly used models are FSM [15] [16], graph model [17], and Extracted Control Flow Machine [18]. The abstract models are either manually constructed from high-level specifications [19] [17] [15] or automatically extracted from the design. Formal methods such as model checking [15] [16], symbolic simulation [20], bounded model checking [21] are used to search the path. For the method to be applicable, the model must be

abstract enough, which affects its ability to be accurate; otherwise, the method can only be applied to relatively small designs.

The main idea behind feedback-based CDTG is to create a system that captures the relationships between coverage and inputs in a simpler but less precise manner and to combine this knowledge with the power of the random stimuli generator to generate inputs that improve the possibility of hitting the target coverage points [14]. Recent works proposed various techniques to learn from the simulation results. These approaches employ a variety of learning techniques such as Bayesian Networks [22], Markov Models [23], Genetic Algorithms [24] and Inductive Logic Programming [25]. However, automatically modifying the input to the test generator, based on the feedback from simulation, can be very difficult for complex designs. The feedback-based CDTG has been an active research area. A recent work in [6] proposed to learn test knowledge from micro-architectural behavior and embed the knowledge into the test generator to produce more effective tests.

## Chapter 3

# Kernel-Based Novelty Detection for Simulation Cost Reduction

#### 3.1 Overview

Novel test detection is an approach to improve simulation efficiency by selecting novel tests before their application [26]. Techniques have been proposed to apply the approach in the context of processor verification [27]. This chapter reports our experience in applying the approach to verifying a commercial processor. Our objectives are threefold: to implement the approach in a practical setting, to assess its effectiveness and to understand its challenges in practical application. The experiments are conducted based on a simulation environment for verifying a commercial dual-thread low-power processor core. By focusing on the complex fixed-point unit, the results show up to 96% saving in simulation time. The main limitation of the implementation is discussed based

on the load-store unit with initial promising results to show how to overcome the limitation.

#### 3.2 Introduction

In a practical simulation-based verification environment, one of the most challenging tasks is to produce the tests that lead to the desired coverage level. One common practice is to manually produce direct tests targeting on specific coverage items. For processor verification, another common approach is constrained random test program generation in which users provide constraints and biases in the form of test templates and directives to the test generator [9]. The input to the test generator specifies the sampling scheme for various dimensions in the test space such as address selection, register dependencies, arithmetic data selection, etc.

Coverage-directed test generation (CDTG) is an emerging approach to overcome the test generation problem. CDTG techniques dynamically analyse coverage results and automatically adapt the test generation process to improve the coverage. Recent works proposed various techniques to learn from the simulation results and improve the test generation. These techniques employ a variety of learning techniques such as Bayesian Networks [22], Markov Models [23], Genetic Algorithms [24] and Inductive Logic Programming [25]. In [28] the authors proposed an automatic target constraint generation technique to alleviate the burden of constraint generation.

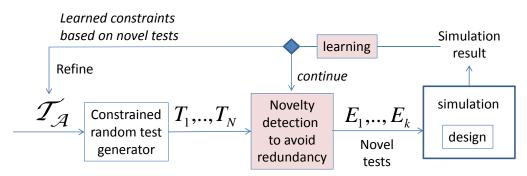

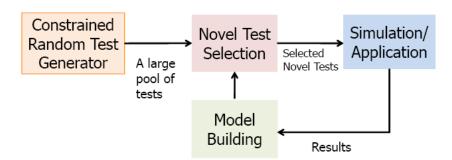

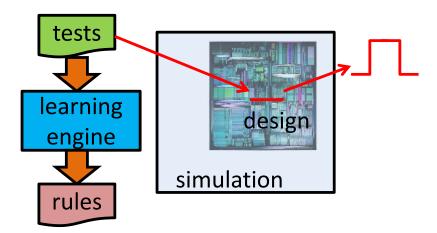

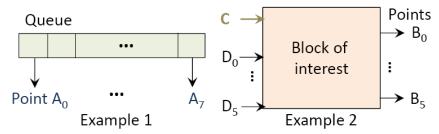

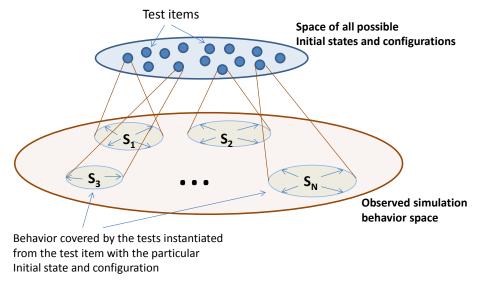

Figure 3.1: Illustration of novel test detection

Novel test detection tries to tackle a problem much more restricted than CDTG. Figure 3.1 illustrates the approach. In a novel test detection framework, the assumption is that there is a constrained random test generator that can instantiate the test template to generate a large number of functional tests. The idea is to learn a novel test detection model based on the results from tests that have already been applied. This model is used to select novel tests from the large pool of tests before their application. Hence, only the selected novel tests are applied, which reduces the simulation cost.

The authors in [26, 29] proposed a novel test detection framework where Support Vector Machine (SVM) one-class algorithm [30] is used to build models. The framework is limited to analysing fixed-cycle functional tests. The authors in [27] extended the application to build novel test detection models where tests are assembly programs and the context is for processor verification. The experiments were conducted based on a rather simple Plasma/MIPS processor design.

The objective of the work in this chapter is not to claim that novel test detection is better than the existing approaches for improving constrained random test generation. In fact, novel test detection can be viewed as complementary to constrained random test generation and to CDTG. Our objective instead is to assess the applicability and effectiveness of novel test detection in a practical setting. We began by implementing the approach proposed in [27] in a company's in-house simulation environment for a dual-thread low-power processor. The experiments were conducted parallel to the ongoing verification efforts.

In this chapter, we explain the main findings based on the commercial experiment. These findings are organized into the remaining flow of the chapter as the following:

- Section 3.3 presents simulation results to illustrate the existence of novel tests in the particular simulation-based processor verification environment.

- Section 3.4 reviews the approach proposed in [27], in particular the *graph-based kernel* method used to measure similarity on a pair of assembly programs. Applying the approach to the complex fixed-point unit demonstrates up to 80% potential saving in simulation time.

- Section 3.5 discusses the major challenge of applying the graph-based kernel approach in practice. To implement the graph-based kernel demands a user to manually implement a cost table defining the similarity between every pair of instructions in consideration. To overcome this challenge, an alternative approach based on estimating coverage of an assembly program is proposed. This alternative approach implements a flow that requires minimal user involvement. The implementation is also easier. We demonstrate that this alternative approach can be as effective as the graph-based kernel approach and delivers up to 96% potential saving in simulation time.

- Section 3.6 discusses the main limitation of the alternative approach and proposes an extension to overcome the limitation. The effectiveness of

this extension is shown based on an experiment on a module in the loadstore unit with a potential 96% saving in simulation time.

• Section 3.7 summarizes this chapter.

# 3.3 The Experimental Framework and Novel Tests

The experiments in this chapter and next chapter were conducted based on a dual-thread low-power 64-bit Power Architecture-based processor core. It was targeted to be manufactured in a 28 nm technology. The processor core supports dual-thread capability that enables each core to act as two virtual cores. Each thread has dedicated Fetch, Decode, Issue, and Completion resources. Each thread also has a dedicated Branch Unit, Load Store Unit, and Simple Fixed Point unit. The Complex Fixed Point unit as well as the Floating Point Unit and the vector engine are shared between threads. The core is designed with a memory subsystem supporting up to an eight-core implementation in a multiprocessing system.

The in-house simulation-based verification environment conforms to a state-of-the-art coverage-driven flow. An in-house test generator is used to generate constrained random test programs based on user-supplied test templates. During the test generation, architectural simulation is also performed and the simulation results are embedded in test programs. The RTL simulation results are compared with the architectural simulation results for checking correctness. The coverage information is recorded and reported using a commercial coverage analysis tool. The verification coverage space is divided into subspaces.

A subspace can be a part of the design, e.g., a particular unit or a specific mechanism such as memory collision, etc. In our experiments, we focused on the toggle coverage of the Complex Fixed Point unit (CFX) and the Load Store Unit (LSU). Test templates targeting on these units are provided by the verification team and are used in constrained random test generation.

#### 3.3.1 Existence of Novel Tests in Practice

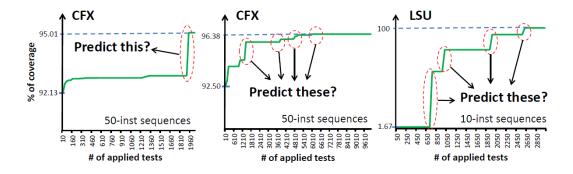

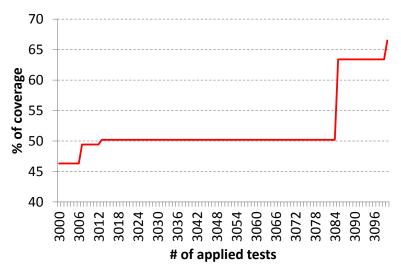

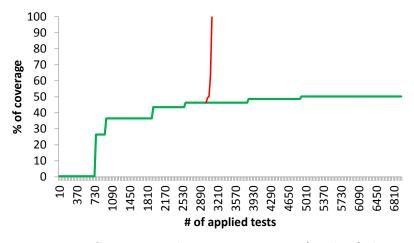

Figure 3.2 shows three plots for three simulation runs, two on CFX and one on LSU. The x-axis shows the number of tests simulated, incremented by 30 at a time. The y-axis shows the normalized coverage based on the maximum coverage achieved for the respective unit in all experiments.

FIGURE 3.2: Three simulation runs to illustrate the existence of novel tests

For the CFX, the first run consists of 2000 test programs each with 50 instructions and an initial machine state. The test programs are instantiated from a template based on 33 instructions targeting on the unit. The second run is similar, consisting of 10K test programs each also with 50 instructions and an initial state. For the LSU, the run consists of 3000 test programs each with 10 instructions and an initial state. The template is based on 6 instructions targeting on the unit.

In all three plots, we observe jumps in the coverage curves. These jumps are due to special tests that provide relatively significant coverage at the given simulation point. These special tests are the novel tests that we are looking for. If they can be identified before simulation, they can be applied earlier in the simulation run. As a result, the respective coverage can be achieved much faster.

Take the first plot as an example. We see that the jump occurs after simulating 1900 tests. We also see that the coverage curve is flat from 1300 to 1900. Suppose an engineer uses the template to instantiate 1600 tests and observes the flat curve. It is likely that the engineer would decide it is not effective to continue. Then, the coverage jump would have been missed. If we have the ability to predict novel tests before simulation, we can generate a much larger number of tests to begin with and consequently reduce the chance of missing a test capable of producing a significant coverage increase.

The three plots in Figure 3.2 show the existence of novel tests in practical simulation-based verification scenarios. This gives a clear motivation to apply novel test detection to identify those tests before simulation.

#### 3.4 The Graph-based Kernel Approach

#### 3.4.1 Kernel Based Learning with SVM One-class

Support Vector Machine (SVM) one-class algorithm, such as the  $\nu$ -SVM algorithm [30] is an unsupervised learning method that builds a model to identify outliers in a given set of samples. The parameter  $\nu$  is a user-supplied input

that represents an upper bound on the number of outliers and low bound on the number of *support vectors*. In application with n samples, we typically set  $\nu$  to be  $\frac{1}{n}$  meaning that we want to build a model to incorporate at least n-1 samples, i.e. with at most one outlier.

In applying  $\nu$ -SVM in novel test selection, the samples are tests that have been simulated up to the point of simulation. Suppose they are  $t_1, ..., t_m$ . A SVM model when applying to an un-simulated test T takes the following form:

$$M(T) = \sum_{i=1}^{m} \alpha_i K(T, t_i) - \rho$$

Conceptually, one can consider each  $\alpha_i$  as a weight denoting the importance of test  $t_i$  in the calculation of the model. A test  $t_i$  is a support vector if  $|\alpha_i| > 0$ . Otherwise, it is a non-support vector, meaning that it is not used in the calculation. The  $\rho$  is a constant denoting the boundary of the measured outlier value for a test T. If M(T) < 0, T is deemed dissimilar to the simulated tests  $t_1, ..., t_m$ . The more negative the M(T) is, the more dissimilar the test T is to  $t_1, ..., t_m$ . Given a set of un-simulated tests  $T_1, ..., T_n$ , let  $M(T_j)$  be the most negative value computed by the model. Then, test  $T_j$  is the most novel test selected by the model.

The function  $K(T, t_i)$  is called a *kernel* function used to measure similarity between T and  $t_i$ , i.e. a pair of tests. The novel tests selected by a SVM model highly depend on the definition of the kernel function. The kernel function dictates the perspective of what novelty means.

Suppose our objective is to cover a set S of coverage items. Suppose test T covers the subset  $S_T$ . Suppose test  $t_i$  covers the subset  $S_{t_i}$ . Intuitively, the

similarity between T and  $t_i$  can be measured as  $\frac{|S_T \cap S_{t_i}|}{|S_T \cup S_{t_i}|}$ . For  $t_i$ ,  $S_{t_i}$  is known. However for T,  $S_T$  is unknown because it has not yet been simulated.

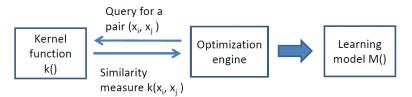

The SVM one-class is a kernel-based learning method [31]. Such a method consists of two components, a kernel function used to measure similarity between a pair of samples and an optimization engine used to build the model. Figure 3.3 illustrates the learning approach.

FIGURE 3.3: Illustration of kernel-based learning

The SVM one-class algorithm concerns how to find the best values for  $\alpha_1, \ldots, \alpha_m$  and  $\rho$ , based on a given kernel function. As shown in Figure 3.3, such an algorithm access the kernel function by querying the similarity between a pair of samples  $x_i, x_j$ . In application, one can alter the kernel definition without changing the SVM algorithm in order to influence the model building process.

## 3.4.2 The Coverage-independent Graph-based Kernel

Developing an appropriate kernel is at the core of applying the kernel-based learning algorithm. In our application, tests are assembly programs. Hence, the kernel function K() needs to measure similarity between a pair of assembly programs. The work in [27] proposes a graph-based kernel that computes a similarity measure by analysing two assembly programs. It is important to note that such a graph-based kernel does not rely on any coverage information by a test in the calculation. Hence, it is a coverage-independent kernel.

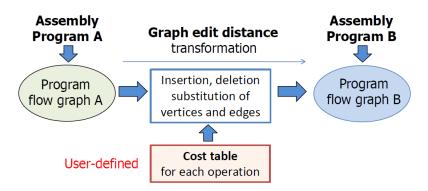

FIGURE 3.4: The framework of computing graph-based kernel

Figure 3.4 illustrates the graph-based kernel. Each assembly program is first converted into a program flow graph, a directed graph capturing the possible execution flows of the program. Then, the kernel calculates the similarity between two programs based on the graph edit distance (GED) of the two graphs. The larger the distance is the more dissimilar the two programs are. The GED is measured as the minimal cost of using a number of operations to transform one graph to the other. These operations include insertion, deletion, and substitution of vertices and edges. Each operation when performed has a cost value. The cost is defined in a cost table. For example, the cost of substitution of an addition instruction to a subtraction is smaller than the cost of substitution of an addition to a load/store instruction. This is because both addition and subtraction utilize the same execution unit while the load/store instruction utilizes the load-store unit.

Because the graph-based kernel is coverage independent, for a given cost table the process of building the model is fixed and consequently the novel tests detected by the model are fixed. This means that in order to apply the graph-based kernel to a given scenario, it is important to have a proper cost table. This cost table can be design dependent, unit dependent and coverage metric dependent. While this provides the flexibility to tackle a variety of scenarios,

it can also be a challenge for its user to develop a proper cost table in practice.

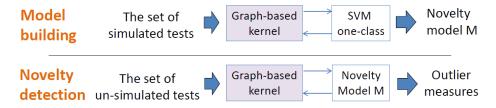

#### 3.4.3 Model Building and Novelty detection

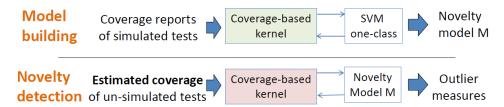

FIGURE 3.5: The framework of graph-based kernel

Figure 3.5 illustrates the model building and novelty detection processes. In model building, a model is built on a set of simulated tests. In novelty detection, the model is applied to a set of un-simulated tests to calculate an outlier measure for each test. These measures are used to rank tests. The most outlying k tests are selected and simulated. For example, the process is iterative as shown in Figure 3.1 where in each iteration the most outlying k tests are selected for simulation.

## 3.4.4 Experiment Results

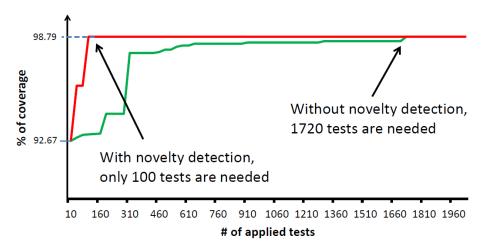

The novel test detection framework using the graph-based kernel approach is implemented and integrated with the in-house simulation environment. Discussions in this section focus on the example shown in the first plot in Figure 3.2, i.e. the case with 2000 test programs for the CFX unit.

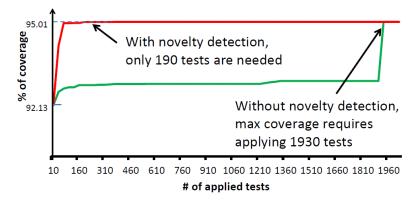

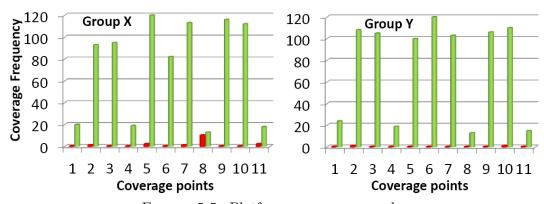

The novel test detection is applied iteratively where each iteration selects 30 tests to simulate from the pool of un-simulated tests. Figure 3.6 compares the coverage curves achieved with and without the novelty detection. The curve without is the same as that shown in Figure 3.2.

FIGURE 3.6: Comparison of coverage curves with and without novelty detection

Without the novel test detection, the original simulation achieves a maximal coverage with 1930 tests. With the novel test detection, the same coverage is achieved using 190 tests, a 90% saving (i.e.  $1-\frac{190}{1930}$ ). The simulation time of 2000 tests is more than a day (using a single machine). This means that with the novel test detection, a day of single-machine simulation time can be reduced to less than two hours.

One may notice the huge coverage jump in the original simulation at around the 1930th test. This indicates a special test whose characteristic is quite different from that of others, i.e. involving a dramatically different sequence of instructions. This might make the novel test detection problem easier. To assess the impact of this special test on the novel test detection, we conduct a different experiment by removing this test from consideration. In this revised experiment, we consider only the first 1800 tests.

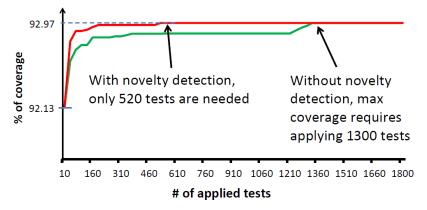

Figure 3.7 shows the results with and without novel test detection based on the 1800 tests. Observe that in this case, the novel test detection can still provide a 60% saving (i.e.  $1-\frac{520}{1300}$ ). The figure also confirms that the existence of the special test does make the novel test detection more effective.

Figure 3.7: Comparison of coverage curves with and without novelty detection based on only the first 1800 tests in Figure 3.6

# 3.5 Kernel Based on Estimated Coverage

#### 3.5.1 Disadvantage of the Graph-kernel Approach

As discussed in Section 3.4.2, the major disadvantage with the graph-based kernel approach is in the manual implementation of the cost table. Figure 3.6 and Figure 3.7 show promising results. However, these results were not obtained without noticeable effort to develop the cost table for verifying the unit. Such a development may take days or weeks to understand the behavior of each instruction with respect to the intended coverage space based on the target unit and/or design. Although one may argue that the development effort can be seen as a one-time cost, in practice, it represents a major obstacle for the acceptance of the approach.

# 3.5.2 Coverage-based Kernel

To ease the use of the novel test detection approach, what we need is a new way to compute the similarity with minimal manual involvement. This motivated us to develop an alternative kernel method based on estimated coverage. Recall from the discussion in Section 3.4.1 that a novelty detection model is of the form:  $M(T) = \sum_{i=1}^{m} \alpha_i K(T, t_i) - \rho$  where  $t_1, \ldots, t_m$  are simulated tests. Such a model is learned based on  $t_1, \ldots, t_m$  to decide the values on  $\alpha_1, \ldots, \alpha_m$  and  $\rho$ . To calculate the similarity between a pair of simulated tests  $t_i, t_j$ , i.e. the kernel denoted as  $K_c(t_i, t_j)$ , we can simply let  $K_c(t_i, t_j) = \frac{|S_{t_i} \cap S_{t_j}|}{|S_{t_i} \cup S_{t_j}|}$ , where  $S_{t_i}$  and  $S_{t_j}$  are subsets of covered items by  $t_i$  and  $t_j$ , respectively. Note that  $t_i, t_j$  are simulated tests and hence,  $S_{t_i}$  and  $S_{t_j}$  are known. Such a calculation can be based on a given set S of items to cover in the simulation. Hence, the kernel calculation only depends on the selection of S that is much easier to obtain than the cost table. For example, S can be the toggled lines in a specific module of interest. As another example, S can be a set of hard-to-cover toggled lines after some initial simulation.

FIGURE 3.8: The framework of coverage-based kernel

Figure 3.8 illustrates the framework using the coverage-based kernel. In model building, a coverage-based kernel works well because the true coverage of each simulated test is available. In novel test detection, the model M is applied to compute an outlier measure for each un-simulated test T. This requires computing  $K_c(T, t_i)$  for each support vector test  $t_i$  where the true coverage of T is not yet known. Hence, to enable the approach, we require a method to estimate coverage for an un-simulated test T.

#### 3.5.3 Estimating Coverage Before Simulation

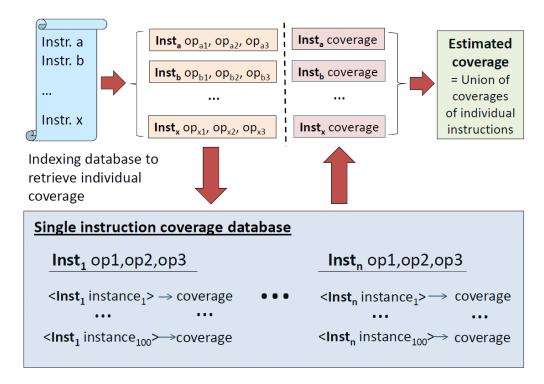

The idea to estimate the coverage of an un-simulated test is simple. Figure 3.9 illustrates the idea.

FIGURE 3.9: Illustration of coverage estimation flow

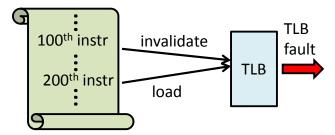

For each single instruction, we randomly instantiated h instances using the constrained random test generation framework. In the experiments, we had h=100. These 100 instances were simulated and their coverages were recorded in a database. There are 600+ instructions defined by the PowerPC ISA. It took about 250 hours to build the entire single instruction coverage database. The storage requirement is about 480GB. The simulation time represents a one-time cost for the approach.

For a given un-simulated program T consisting of a sequence of instructions, for each instruction I we retrieve the coverage from the database based on the instruction instance that is closest to the instruction I. This closeness is decided based on an *indexing function*. We implemented the indexing function to look for the closest instruction instance based on Hamming-distance calculation between the operand values of the instruction I in T and the operand values of the instruction instances stored in the database. For each instruction I in T, the indexing function decides the closest instruction instance in the database. Then, the corresponding coverage is retrieved and used for I. To estimate the coverage of T, we simply take the union of all the retrieved coverages.

It is important to note that using the union operation to estimate the coverage presents a major limitation to the approach. This limitation will be discussed in Section 3.7 later.

### 3.5.4 The Accuracy of Coverage Estimation

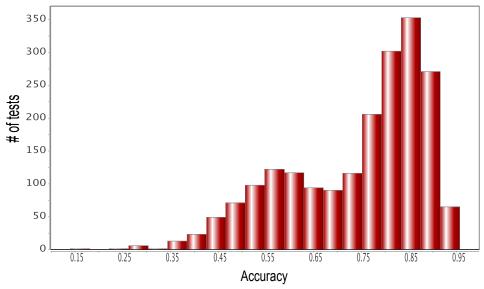

To give an idea on the accuracy of the coverage estimation method, Figure 3.10 shows a result based on the 2000 test programs used in the experiment in Figure 3.6. The x-axis shows the accuracy measured in terms of the percentage of overlap between the estimated coverage and the true coverage of a test program. The average estimation accuracy is around 75% and is far from being perfect. Later in the experimental section 3.5.6, we will show that this accuracy is sufficient for novel test detection to be effective.

Figure 3.10: Histogram of estimation accuracy of 2000 tests

#### 3.5.5 Dynamically Adjusting the Coverage Base Set S

In Section 3.5.2, we discuss the flexibility of the coverage-based kernel method. The coverage is estimated based on a set S of coverage items where this set can be flexibly defined. We call such a set the *coverage base set*.

Recall that novel test detection is an iterative process. Hence, ideally in each iteration the perspective of novelty should be defined with respect to the uncovered items. In other words, the novelty of a test should be evaluated based on its chance to provide coverage on the uncovered items.

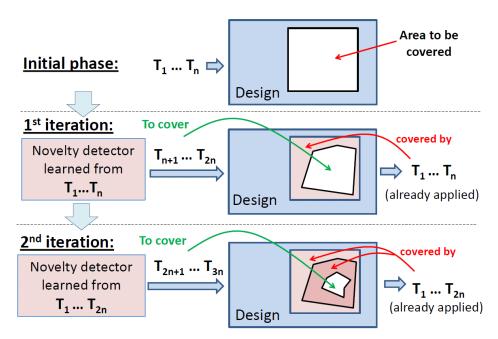

Figure 3.11 illustrates the iterative process. Initially, a set of tests  $T_1, ..., T_n$  are simulated. Then a novel test detection model  $M_0$  is learned from the coverage results of  $T_1, ..., T_n$ . When applying  $M_0$  to select the next n novel tests  $T_{n+1}, ..., T_{2n}$ , we would like to cover the uncovered area in the design. To achieve this effect, we can perform the following adjustment on the coverage base set S.

FIGURE 3.11: An ideal iterative process with novel test detection

Initially, suppose the set S contains p items  $c_1, \ldots, c_p$ . Let each item  $c_i$  be associated with a weight  $w_i$  initialized as 1. We calculate the coverage as  $\sum w_i$  for all i such that  $c_i$  is covered by a test. Every time  $c_i$  is covered,  $w_i$  is adjusted to  $w_i/a$  where a is a constant such as a=2. Such a weight adjustment scheme depreciates the importance of a covered item gradually.

Similarly, after the first iteration, a novel test detection model  $M_1$  is learned based on all the simulated tests  $T_1, ..., T_{2n}$ . This model  $M_1$  is used to select the next n novel tests  $T_{2n+1}, ..., T_{3n}$  for hitting the uncovered area.

It is important to note in model building, those uncovered items do not participate in the coverage-based kernel calculation. This is because in model building, the true coverage of simulated tests is used and an uncovered item is skipped in the coverage calculation. When the model is applied to estimated coverage for an un-simulated test, an uncovered item may participate in the kernel calculation. This is because it is possible that the instruction instances retrieved from the database can hit the uncovered item.

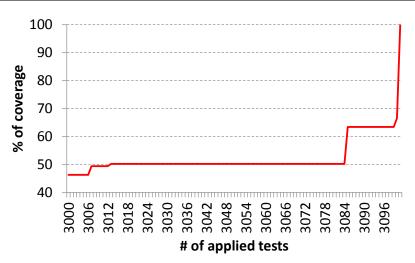

### 3.5.6 Results Compared to the Graph-based Kernel Method

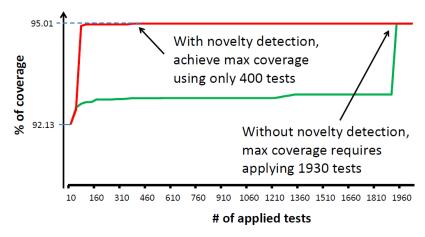

FIGURE 3.12: Comparison of coverage curves with and without novelty detection using the coverage-based kernel; The same example shown in Figure 3.6

Figure 3.12 shows the result based on the same example shown in Figure 3.6. Again, in each iteration the top 30 novel tests are selected for simulation. We see that with the novelty detection, only 400 tests are required to achieve the same coverage of using 1930 tests in the original simulation run, an 80% saving. Comparing this result to that shown in Figure 3.6, we observe the effectiveness is not as good as before. However, 80% remains a significant saving.

Figure 3.13: Comparison of coverage curves with and without novelty detection using the coverage-based kernel; The same example shown in Figure 3.7

Figure 3.13 shows the result based on the same example shown in Figure 3.7 before, i.e. using only the first 1800 tests by removing the one special test giving the big coverage jump at the 1930th test in the original simulation run. We see that with the novelty detection, only 220 tests are required to achieve the same coverage of using 1300 tests in the original simulation run, an 83% saving. Comparing this result to the 60% saving shown in Figure 3.7, the effectiveness is better than before.

#### 3.5.7 Result on Simulation of 10K Tests

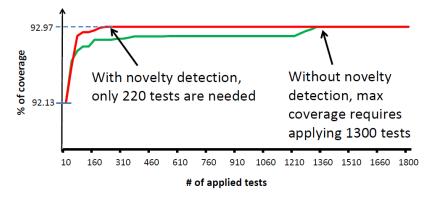

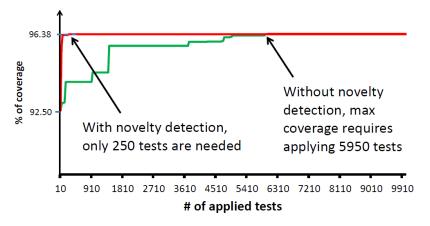

Figure 3.14: Comparison of coverage curves with and without novelty detection based on the middle plot example shown in Figure 3.2 before

Figure 3.14 demonstrates the effectiveness of novel test selection using the coverage-based kernel for the 10k tests simulation example shown in Figure 3.2. Without novelty detection, the maximal coverage of the original simulation run is achieved with 5950 tests. With novelty detection, the same coverage is achieved using only 250 tests, or roughly a 96% saving. Simulation of the 5950 tests would have taken more than 4 days of single-machine simulation time. With the novelty detection, this time is reduced to less than 6 hours.

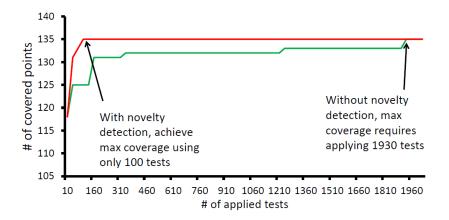

#### 3.5.8 Two Additional Results

To show that the novelty detection approach can work well on tests based on a focused instruction base, we conducted an experiment using a test template based on only 6 CFX instructions. 2000 test programs were instantiated each with 50 instructions and an initial state. Figure 3.15 shows the results with and without novelty detection. Without the novelty detection, the original simulation achieves the maximal coverage with 1720 tests. With the novelty detection, the same coverage is achieved with only 100 tests, i.e. a 94% saving.

FIGURE 3.15: Results based on 2000 tests instantiated from 6 CFX instructions

To show that the novelty detection can also work well on selected coverage points, we conducted an experiment by focusing on the 200 hard-to-cover points in the CFX unit. 2000 tests of 50 instructions were simulated in the original run. Without the novelty detection, the original simulation achieves the maximal coverage with 1930 tests. With the novelty detection, the same coverage is achieved with only 100 tests, i.e. a roughly 95% saving.

FIGURE 3.16: Results based on 200 hard-to-cover points in CFX

## 3.6 Limitation of the Single-Instruction Database

Section 3.5.3 discusses the method to estimate coverage for an un-simulated test program and points out its major limitation is in the use of the union operation to compute the coverage (also see Figure 3.9 for this union operation). Because the estimated coverage of a test program is the union of individual estimated coverages of all the instructions in the test program, such an estimated coverage does not consider coverage contributed by multiple instructions collectively. This limits the application of novelty detection to, for example, the load-store unit consisting of multiple finite-state machines, arrays and register files. For example, a data-forwarding event occurs when Read-After-Write hazards are present. Using the single-instruction database would be unable to properly estimate the coverage given by a test containing such hazards.

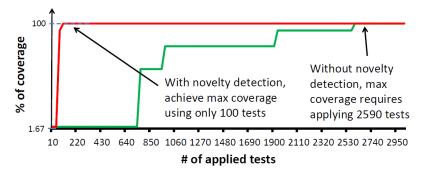

The LSU is one of the most complex units in the design. It is responsible for scheduling and managing the out-of-order memory operations. To illustrate the idea for overcoming the limitation we focus on an experiment based on the data-forwarding module used in the store queue. The result of the original simulation run is shown in the third plot in Figure 3.2. Below we discuss how

to refine the novelty detection implementation to capture those novel tests shown in the plot.

The idea is simple. To overcome the limitation of using the single-instruction database, we build a database with a large number of test program instances each consisting of three instructions. Then, we use the coverage information stored in this 3-instruction database to estimate the coverage of test programs with a longer length. The indexing function in Figure 3.9 needs to be modified. In other words, the estimated coverage of a 10-instruction test becomes the union of coverages of several 3-instruction instances retrieved from the database.

Figure 3.17 shows the result of applying this extension to the particular example. Without novelty detection, the original simulation achieves the maximal coverage with 2590 tests. With novelty detection, the same coverage is achieved with only 100 tests, a 96% saving. Again, the coverage shown on y-axis is normalized based on the coverage achieved in the particular example and hence, it is shown as 100%.

FIGURE 3.17: Comparison of coverage curves with and without novelty detection using extended coverage-based kernel based on the third example plot shown in Figure 3.2

## 3.7 Summary

In this chapter, we report the experience of applying novel test detection in a company in-house constrained random test generation and simulation environment for a Power architecture-compliant processor core. The first implementation is based on the graph-based kernel method. While this implementation can demonstrate 60-90% saving of simulation time, its practical applicability is limited because of the requirement to manually construct the cost table. To overcome this limitation, a second implementation is proposed. This alternative approach is based on a coverage-based kernel method. The effectiveness of this approach is comparable to the graph-based kernel approach. The alternative approach demands minimal user involvement and hence is much more acceptable in practice. With the second implementation, we demonstrate 80-96% simulation cost reduction in various experiments. In one case, more than four days of single-machine simulation time can be reduced to less than six hours.

We discuss an extension based on the second implementation. The extension overcomes the limitation of using the single-instruction database to estimate coverage. A new database of 3-instruction instances is added to capture coverage depending on multiple instructions collectively. The effectiveness of this extension is demonstrated on the data-forwarding module in the LSU with a potential 96% saving in simulation time.

# Chapter 4

**Knowledge Extraction**

Framework to Improve

Functional Verification Coverage

### 4.1 Overview

This chapter proposes a methodology of knowledge extraction from constrained random verification data. Feature-based analysis is employed to extract rules describing the unique properties of novel assembly programs hitting special conditions. The knowledge learned can be reused to guide constrained random test generation towards uncovered corners. The experiments are conducted based on the verification environment of a commercial processor design, in parallel with the on-going verification efforts. The experimental results show

that by leveraging the knowledge extracted from constrained random simulation, we can improve the test templates to hit the functional events that otherwise are difficult to hit by extensive simulation.

### 4.2 Introduction

In a design cycle, the design evolves over time. Consequently, functional verification is an iterative process in which extensive simulation is run on a few relatively stable versions of the design. When a new version is released with accumulated changes over a period, the verification process restarts with the new version. From one iteration to another, two assets are kept. The first are the test templates refined and accumulated up to the previous iteration. The second are the "novel" tests (as described in Chapter 3) identified so far. For example, a novel test can be the one hitting a particular block and/or event of interest or capturing a bug in the previous design versions. These two assets embed the knowledge accumulated through the iterative verification process.

In this chapter, we propose a novel learning methodology for extracting knowledge from novel tests. The extracted knowledge then is reused for two purposes: (1) for producing more tests similar to those novel ones and (2) for producing new novel tests that, for example, can hit blocks and/or events not covered before. To develop such a learning methodology, we need to address three aspects: (1) what knowledge to extract, (2) how to extract and represent knowledge, and (3) how to reuse the extracted knowledge.

We applied the proposed methodology to verifying a dual-thread low-power 64bit Power Architecture-based processor core to be manufactured with a 28nm technology. Our experiments were conducted parallel to the verification process where the design was not yet stable. The experimental results demonstrate the effectiveness of the methodology for the two intended purposes. More specifically, we show that after applying the extracted knowledge, a refined test template can effectively generate additional tests for hitting a block and/or functional event that received low coverage before. Moreover, a refined test template can effectively generate tests for hitting an event that was not covered before.

The rest of the chapter is outlined as follows: Section 4.3.1 presents a motivational example for this work. Section 4.3.2 addresses the first aspect, i.e. what knowledge to extract. Section 4.3.3 briefly reviews the related works. A feature-based rule learning methodology is presented in Section 4.4 to address the knowledge representation aspect. Section 4.5 discusses the knowledge extraction aspect using subgroup discovery rule learning. Section 4.6 illustrates how the knowledge can be reused. Section 4.7 discusses the possible adaptations to enhance the methodology. Experimental results are presented in Section 4.8. Section 4.9 summarizes the chapter.

# 4.3 Motivation and Related Works

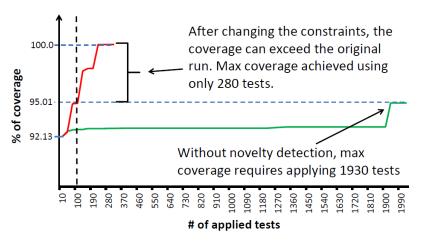

## 4.3.1 The Benefits of Understanding Novel Tests

Figure 3.12 in Chapter 3 shows that the special test causing a coverage jump at about the 1930th test in the original simulation is captured by novel test detection within the first 100 tests. It is interesting to understand why the special test can cause such a coverage jump. We analysed the special test

in Figure 3.12 based on a set of features such as instruction types, operand values and the changes of those values in a program. A property we learned is that there is an exception in the novel test that does not occur in non-novel tests. Also, there are move-to-special-register instructions in the novel test, which don't appear elsewhere. We examined the novel test and found the exception triggers an interrupt routine and the special instructions are part of the interrupt routine. Then we modified the test templates to produce more tests satisfying the property and observed the coverage impact.

Figure 4.1: Improving coverage by test template refinement

Figure 4.1 shows the result of this test template refinement. After simulation of the first 100 tests, the special test that results in a coverage jump is identified. After understanding the unique properties of the special test, the test template is manually modified to produce additional tests. Observe that the additional 180 tests are able to improve the coverage to exceed that achieved by the original 2000 tests. The y-axis is normalized based on the maximal coverage achieved, and that is why the best coverage shown is 100%. Note that this maximal coverage is the best coverage achieved across all experiments on the CFX unit in this dissertation and all coverages for CFX shown in Chapter 3 are normalized based on this best coverage. The result shows us that we can

achieve additional coverage benefits beyond novel test detection by extracting knowledge from the novel tests to refine the test template.

#### 4.3.2 What Knowledge to Extract

The example in Section 4.3.1 illustrates a scenario where structural coverage such as toggle coverage is concerned. In more occasions, functional coverage is more of a concern. During the design iteration, it may not be effective to maintain the detailed structural coverage results from one iteration to the next due to major changes in the implementation. Therefore, functional coverage is often used as the metric to evaluate the importance of tests and to guide test template refinement. The definitions of the functional events are relatively stable and do not change as often as the design implementation. Hence, the majority of the purpose for knowledge extraction in this chapter is to improve functional coverage, although as we will demonstrate by experimental results, it can also improve structural coverage.

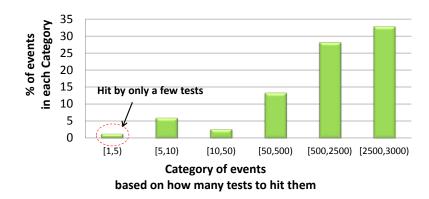

Figure 4.2 illustrates a scenario of simulation with tests instantiated from a given test template that had been refined by the verification team up to the time of the experiment. The figure summarizes the statistics of covered functional events for the Load Store Unit (LSU) of the processor in a simulation of 3000 tests. The LSU is among the most complex and difficult-to-verify units in the design. Over 90% of the covered events were already hit by 50 or more tests. However, there existed other events activated only by 10 tests or fewer. Furthermore, there were events with zero coverage (not shown in the figure).

Our interest is in knowledge extraction for hitting those events with low or zero coverage. The property stated by a complex event comprises multiple

FIGURE 4.2: Histogram of covered events in LSU based on the frequency of being hit

conditions. Learning the knowledge about the entire event directly could be difficult. Hence a divide-and-conquer strategy is employed. The idea is to learn knowledge with respect to each condition and then, the knowledge can be combined for hitting the event. The similar thinking applies to improving the structural coverage of a block since hitting a block usually depends on the activation of certain conditions.

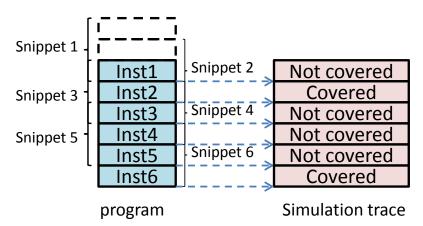

Knowledge extraction for a given condition is based on tests activating the condition. We call those tests the *novel* tests. In processor verification, a test is an assembly program. Figure 4.3 illustrates the learning goal. Suppose a novel assembly program is identified to trigger a special condition in the simulation, for example, a "coreflush" condition concerning the instructions already fetched but not yet committed. Then what we want to learn are descriptive *rules* explaining the properties in the novel tests that trigger the condition, for example, the rule being the existence of a mis-predicted branch in the test. Such rules are then used as constraints to refine test templates for hitting the condition.

To summarize, in our methodology we begin by monitoring a set of conditions. Novel tests with respect to these conditions are identified and recorded in the

FIGURE 4.3: Illustration of the learning goal

simulation. The extracted knowledge is rules describing the special properties of the novel tests.

#### 4.3.3 Related Works

In a feature-based diagnosis approach, a set of features are used to encode the characteristics of a sample (in our case a sample is a test). This encoding transforms each sample into a feature vector. Then, by analysing the feature vector of a special sample against other non-special samples, we can extract rules to explain the unique property of the special sample, e.g. the special sample satisfies the rule and all other samples do not. For the rule extraction analysis, one can use a decision tree algorithm [32] or the subgroup discovery algorithm [33]. Feature-based rule learning has been applied in the context of understanding design-silicon mismatch [34]. In our work, we apply the approach to analyse the special test to understand its specialty. In contrast, this chapter studies the feasibility and effectiveness of applying feature-based analysis for extracting knowledge from novel tests to improve verification coverage.

### 4.4 Feature Generation

#### 4.4.1 Snippet-based Vector Representation