#### UNIVERSITY OF CALIFORNIA Santa Barbara

### Realization and Formal Analysis of Asynchronous Pulse Communication Circuits

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Merritt Philip Miller

#### Committee in Charge:

Professor Forrest Brewer, Chair

Professor Luke Thogarajan

Professor Li-C. Wang

Professor Tevfik Bultan

March 2015

## The dissertation of Merritt Philip Miller is approved:

Professor Luke Thogarajan

Professor Li-C. Wang

Professor Tevfik Bultan

Professor Forrest Brewer, Committee Chairperson

December 2014

Realization and Formal Analysis of Asynchronous Pulse Communication Circuits

Copyright © 2015

by

Merritt Philip Miller

Dedicated to the person crazy enough to follow in my footsteps

#### Acknowledgements

There are many people I wish to thank, without whom my research and this dissertation would not be possible. While an exhaustive list would be prohibitive I would like to thank a number of people who were instrumental in this work and me completing my degree. Forrest Brewer, as an advisor and mentor, who's guidance and input made possible so many developments. Luke Thogarajan, Li-C. Wang, Tevfik Bultan, for serving as my committee and all of the useful advice. Joseph Incandella and Guido Magazzu for the research opportunities and introduction to the world of electronics for high-energy physics. I would like to thank everyone I have worked with in the lab, Greg, Nittin, Amitabh, Kunal, Wei, Joseph, Ethan, Alec, Dan, Di, and Carrie. Most importantly I owe an amazing debt of gratitude to Mom, Dad, Sab and Whitney; With out your love and support it would not be possible to finish this life-consuming endeavor.

I would like to thank the Department of Energy for their generous funding of the grant DOE-CERN CMS SLHC "Protocols and IP-Cores for Control and Readout in Future Higher Energy Physics Experiments" Which provided needed support for much of the presented work.

#### Curriculum Vitæ

#### Merritt Philip Miller

#### Education

2015 Ph.D. in Electrical and Computer Engineering (Expected), University of

California, Santa Barbara.

2009 M.S. in Electrical and Computer Engineering, University of California,

Santa Barbara.

2007 B.S. in Electrical Engineering, University of California, Santa Barbara.

#### Publications

Miller, M.; Hoover, G.; Brewer, F., "Pulse-mode link for robust, high speed communications,"

Circuits and Systems, 2008. ISCAS 2008. IEEE International Symposium on , vol., no.,

pp. 3073-3077, 18-21 May 2008

doi: 10.1109/ISCAS.2008.4542107

Miller, Merritt; Brewer, Forrest, "Formal verification of analog circuit parameters across variation utilizing SAT," Design, Automation & Test in Europe Conference & Exhibition (DATE), 2013, vol., no., pp. 1442-1447, 18-22 March 2013

doi: 10.7873/DATE.2013.294

Miller, M.; Brewer, F.; Magazzu, G.; Wang, D., "Multi-gigabit low-power radiation-tolerant data links and improved data motion in trackers" *Journal of Instrumentation* vol. 9, no.

12, pp. C12011 December 2014

doi: 10.1088/1748-0221/9/12/C12011

#### Abstract

#### Realization and Formal Analysis of Asynchronous Pulse Communication Circuits

#### Merritt Philip Miller

This work presents an approach to constructing asynchronous pulsed communication circuits. These circuits use small delay elements to introduce a gate level sense of time, removing the need for either a clock or handshaking signal to be part of a high-speed communication link. This construction method allows the creation of links with better than normal jitter tolerance, allowing for simple circuit architectures that can easily be made robust to radiation induced soft error.

A 5Gbps radiation-hardened link, targeted at use in detector modules at the LHC, will be presented. This application presents a special challenge due to both very high radiation levels (1 + MGy) life time dose) and the demand for minimum resource (area, power, cable cost) use. The presented link, realized in 130nm technology, is unique in that it has low power (50mW) end to end) and very low area  $0.12mm^2$  including electrostatic discharge protection, and I/O amplifiers. Due to its asynchronous construction and the gate design style, the link has essentially zero power dissipation when idle, and enters and exits its idle state with no delay.

In addition to the construction of the link, this presentation covers the design and analysis methodology that can be used to create other asynchronous communication circuits. The methodology achieves higher performance than conventional static technology but needs only a reasonable design effort using tools and strategies that are only mildly extended versions of those familiar to digital static designers. It is used to construct the serializer, describing, and

self-test circuitry for the presented link. In this case, a 5Gbps SER/DES and a 2GHz parallel pseudo-random number generator are implemented in 130nm CMOS technology using a gate design style that does not dissipate static power.

## Contents

| Curriculum Vitae |                           |                                                    |                                                 | vi                               |  |  |

|------------------|---------------------------|----------------------------------------------------|-------------------------------------------------|----------------------------------|--|--|

| $\mathbf{Li}$    | List of Figures           |                                                    |                                                 |                                  |  |  |

| Li               | st of                     | Tables                                             | 3                                               | xiv                              |  |  |

| 1                | Intr<br>1.1<br>1.2<br>1.3 | Philose<br>Radiat<br>1.3.1                         | hronous Pulse Logic                             | 1<br>2<br>6<br>7<br>8            |  |  |

|                  | 1.4                       | 1.3.2<br>Permis                                    | Radiation environment issues in sub-micron CMOS | 9<br>10<br>11<br>13<br>13        |  |  |

| 2                | Svs                       | temati                                             | c Asynchronous Design                           | 15                               |  |  |

| _                | 2.1                       |                                                    | uction                                          | 15<br>17<br>18                   |  |  |

|                  | 2.2                       | On-Ch<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5 | Case Study 5mm wire 130nm process node          | 18<br>20<br>20<br>21<br>22<br>24 |  |  |

|                  | 2.3                       | Compo<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4          | Terminology                                     | 25<br>25<br>26<br>26<br>27       |  |  |

|   | 2.4 | System Description                                                                |

|---|-----|-----------------------------------------------------------------------------------|

|   |     | 2.4.1 Language                                                                    |

|   |     | 2.4.2 Control Data Flow Graph                                                     |

|   |     | 2.4.3 3-bit Counter Example                                                       |

|   | 2.5 | Gate construction                                                                 |

|   |     | 2.5.1 Pull-down network timing                                                    |

|   |     | 2.5.2 Pulse timing                                                                |

|   |     | 2.5.3 Drive and Feed-back network                                                 |

|   | 2.6 | Data Link Performance Estimation                                                  |

|   | 2.7 | Design Methodology Conclusion                                                     |

| 3 | SAT | C based steady state analysis 47                                                  |

| • | 3.1 | Formal Verification of Analog Circuit Parameters and Variation Utilizing SAT . 48 |

|   | 3.2 | Verification                                                                      |

|   | 3.3 | Mapping to SAT                                                                    |

|   | 3.4 | Device Models                                                                     |

|   | 0.1 | 3.4.1 Linear devices                                                              |

|   |     | 3.4.1.1 Current sources                                                           |

|   |     | 3.4.1.2 Voltage sources                                                           |

|   |     | 3.4.1.3 Resistors                                                                 |

|   |     | 3.4.2 Non-linear devices                                                          |

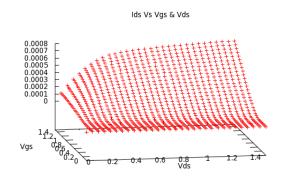

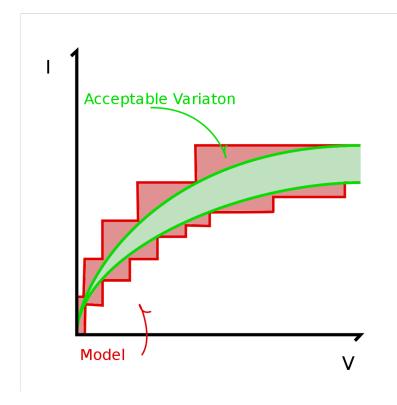

|   |     | 3.4.2.1 Spice/Monte-Carlo Extraction based models                                 |

|   |     | 3.4.2.2 ASU PTM Corner-case transistor curve based model set 62                   |

|   |     | 3.4.3 Model impacts on problem complexity                                         |

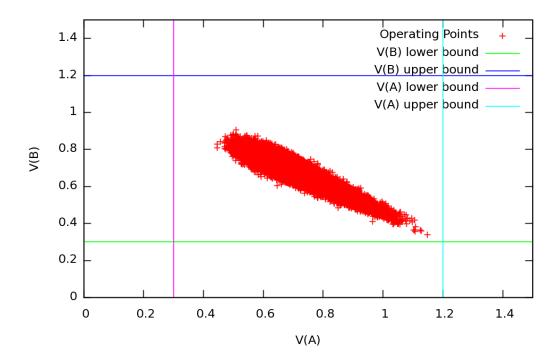

|   | 3.5 | Applied cases                                                                     |

|   | 3.3 | 3.5.1 Resistor divider – output voltage                                           |

|   |     | 3.5.2 Differential amplifier – minimum bais to support drive current 64           |

|   |     | 3.5.3 SRAM characterization                                                       |

|   |     | 3.5.3.1 Meta-stable region                                                        |

|   |     | 3.5.3.2 Stable state                                                              |

|   |     | 3.5.4 SRAM array                                                                  |

|   | 3.6 | Application to pulse circuits                                                     |

|   | 0.0 | 3.6.1 Minimum input voltage                                                       |

| 4 | Imp | plementation and Circuit Characterization 73                                      |

| - | 4.1 | Optimal Wire Width and The Utility Metric                                         |

|   | 1.1 | 4.1.1 Wire Width and Spacing for Maximum Utility                                  |

|   |     | 4.1.2 Delay Based Metric                                                          |

|   |     | 4.1.3 Jitter Based Metric                                                         |

|   |     | 4.1.4 Optimal Utility - Big Picture                                               |

|   | 4.2 | Radiation Damage Modeling for Cell Characterization                               |

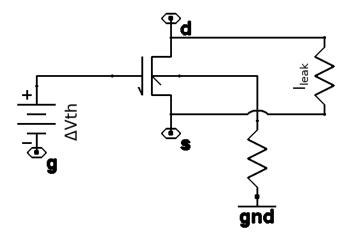

|   | 1.4 | 4.2.1 Gate Threshold Shift                                                        |

|   |     | 4.2.2 Leakage channel                                                             |

|   | 4.3 | Electronics for radiation test                                                    |

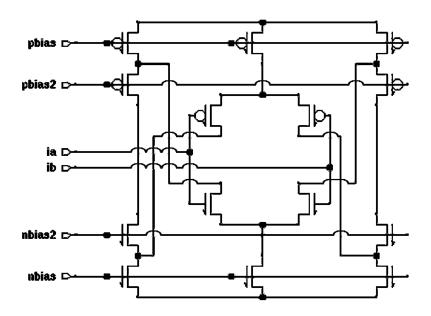

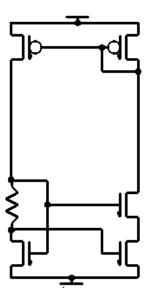

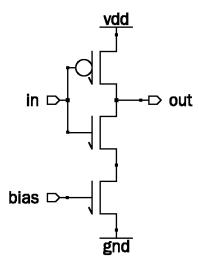

|   | 1.0 | 4.3.1 Upset Hardened Current Source                                               |

|   |     | r                                                                                 |

|    |       | 4.3.2   | Radiation monitoring ring oscillator  | 84  |

|----|-------|---------|---------------------------------------|-----|

| 5  | Link  | c Desig | çn                                    | 86  |

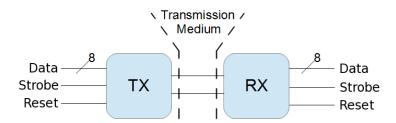

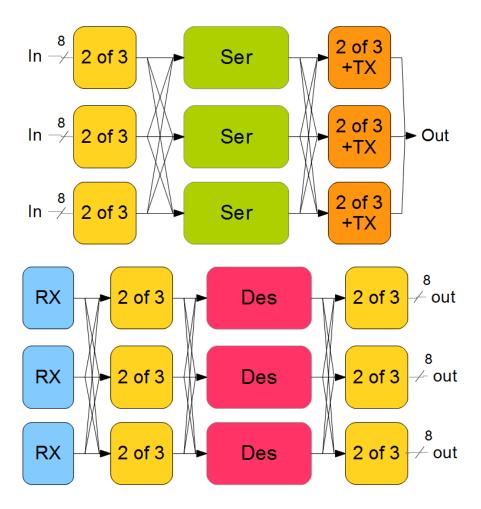

|    | 5.1   | Archite | ecture                                | 86  |

|    |       | 5.1.1   | System interface                      | 87  |

|    |       | 5.1.2   | Implementation of Triplication        | 87  |

|    |       | 5.1.3   | Clock and Reset Triplication          | 88  |

|    | 5.2   | Encodi  | ing                                   | 88  |

|    |       | 5.2.1   | Timing constraints for pulse encoding | 92  |

|    |       | 5.2.2   | Transmission Medium Considerations    | 93  |

|    | 5.3   | Link L  | atency                                | 94  |

|    | 5.4   | Design  |                                       | 95  |

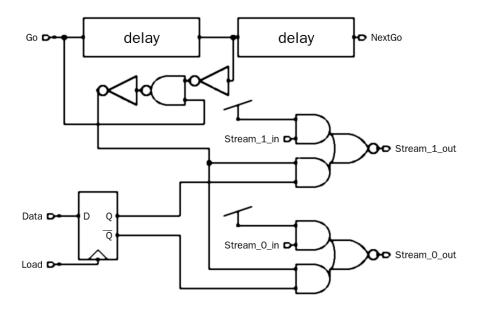

|    |       | 5.4.1   | Serializer                            | 95  |

|    |       | 5.4.2   | Deserializer                          | 96  |

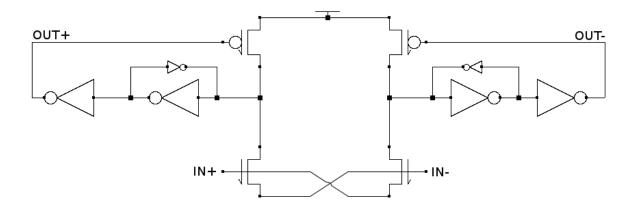

|    |       | 5.4.3   | Transmitter and Receive amplifier     | 99  |

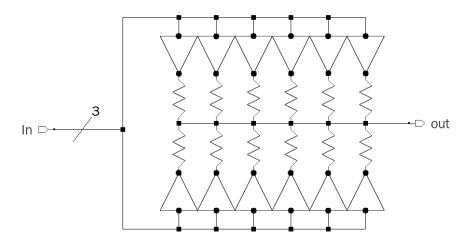

|    |       | 5.4.4   | Driver segmentation                   | 101 |

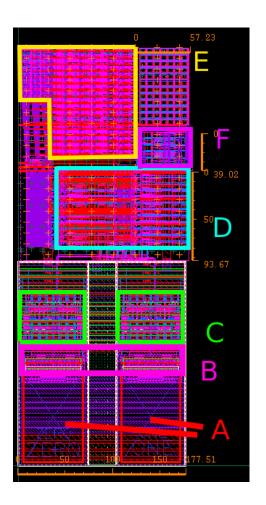

|    | 5.5   | Layout  | ·                                     | 101 |

|    | 5.6   |         | ted Performance                       | 103 |

| 6  | Test  | and I   | Data                                  | 107 |

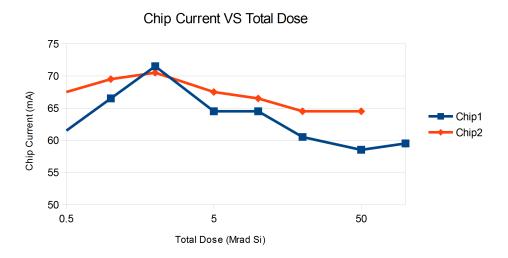

|    | 6.1   | Radiat  | ion Testing and Characterization      | 107 |

|    | 6.2   |         | Link Testing                          | 109 |

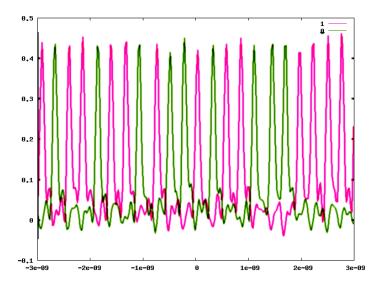

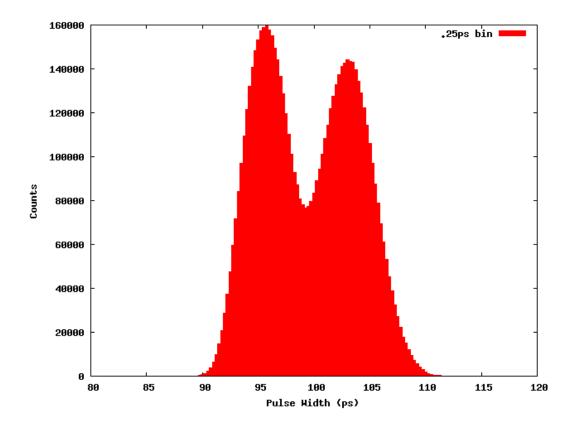

|    |       | 6.2.1   | Output Pulse Characterization         | 113 |

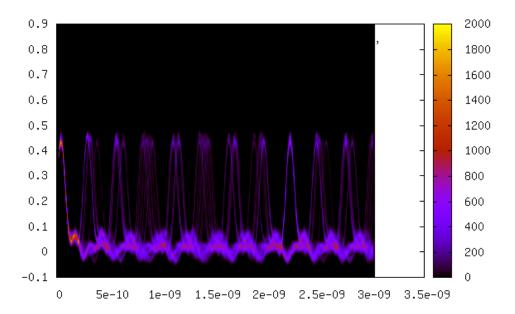

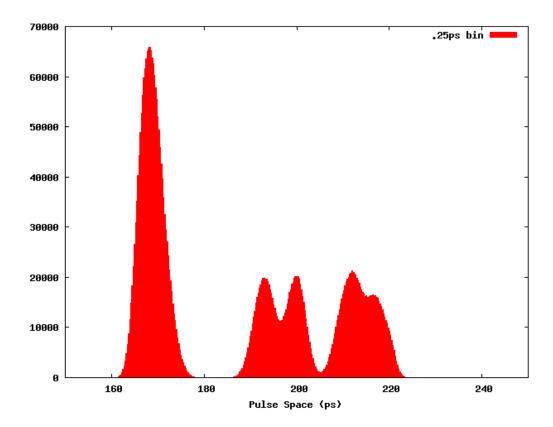

|    |       | 6.2.2   | Pulse Timing Accuracy                 | 117 |

|    |       | 6.2.3   | Power                                 | 121 |

| 7  | Con   | clusion | 1                                     | 122 |

|    | 7.1   | Future  |                                       | 122 |

| Bi | bliog | raphy   |                                       | 125 |

# List of Figures

| 1.1  | An asynchronous pulse stream                                    |

|------|-----------------------------------------------------------------|

| 1.2  | Layout of a cell with additional contact for radiation hardness |

| 2.1  | Control Data Flow Graph elements for pulse logic analysis       |

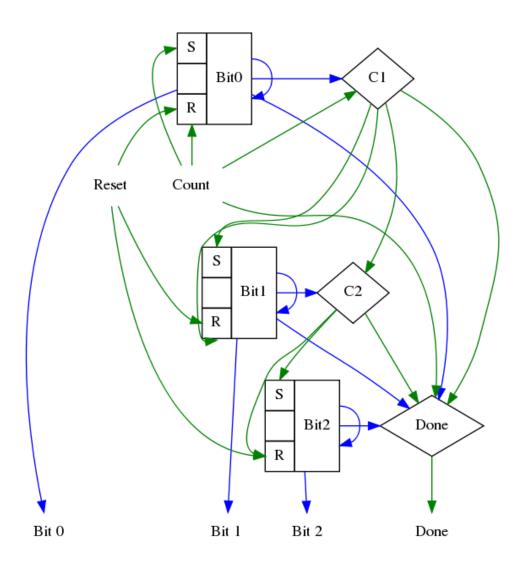

| 2.2  | 3-bit counter without gated events                              |

| 2.3  | 3-bit counter with gated events                                 |

| 2.4  | Drawing of a P-Gate                                             |

| 2.5  | Drawing of a D-Gate                                             |

| 2.6  | Timing diagram for a SR latch                                   |

| 2.7  | Pulse detectability                                             |

| 2.8  | Two self-reset feed-back network options                        |

| 2.9  | Feedback network output pulse comparison                        |

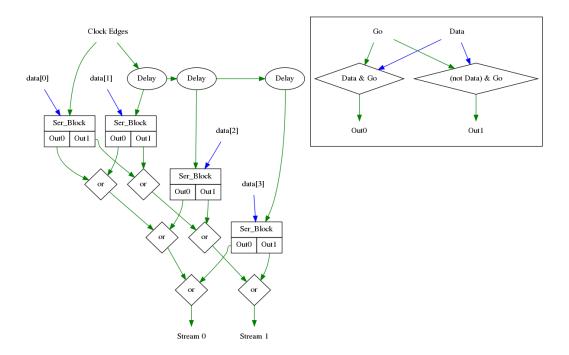

| 2.10 | Simple Serializer Design                                        |

| 2.11 | Descrializer matching the serializer in Figure 2.10             |

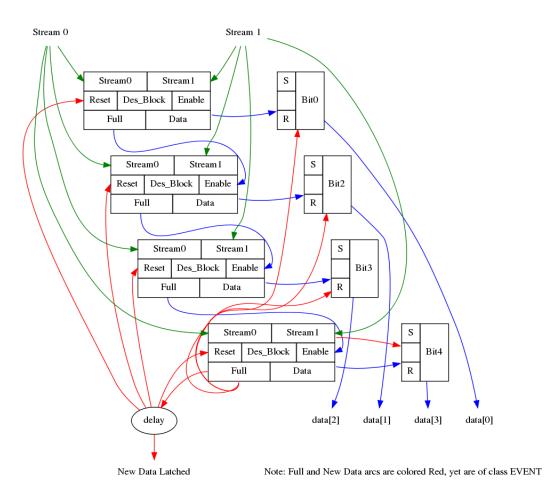

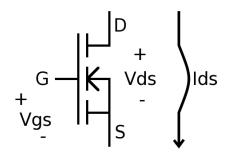

| 3.1  | Example hard-to-solve circuit                                   |

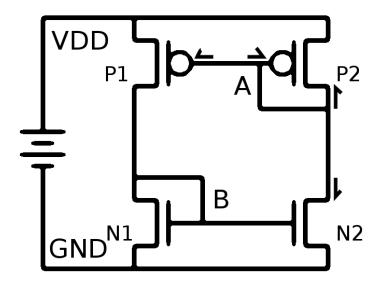

| 3.2  | Field effect transistor                                         |

| 3.3  | Map of verification results for circuit in Fig.3.1              |

| 3.4  | Transistor variation and union of polytope model 61             |

| 3.5  | Differential amplifier with multiple bias points                |

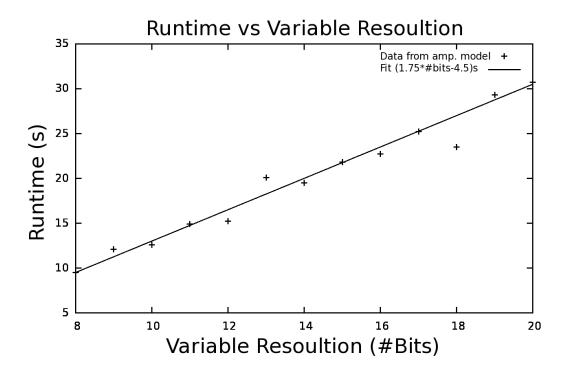

| 3.6  | Solution time vs resolution (log precision)                     |

| 3.7  | SRAM cell                                                       |

| 3.8  | Schematic of SRAM array test                                    |

| 3.9  | P-Gate Used for Pull-Down and Reset Analysis                    |

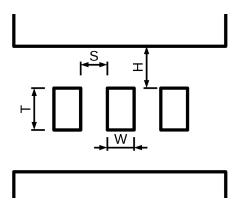

| 4.1  | Critical Dimensions of On-Chip Wiring                           |

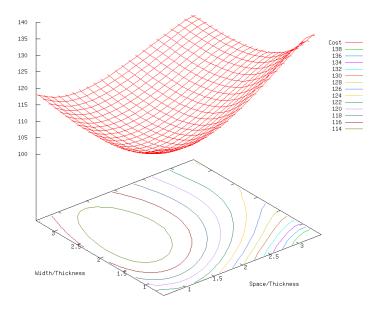

| 4.2  | Relative cost of different wire dimensions                      |

| 4.3  | Damaged FET Electrical Model                                    |

| 4.4  | Test upset hardened current source                              |

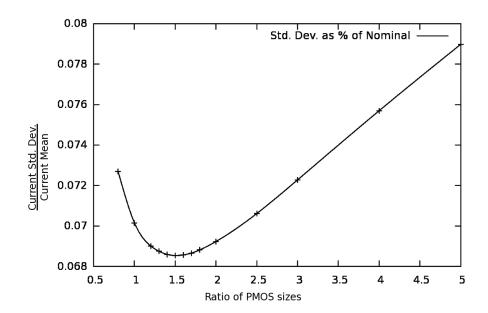

| 4.5  | Optimization curve for PMOS ratio                               |

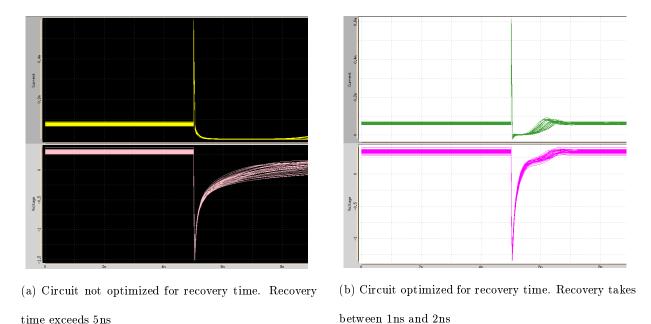

| 4.6  | Simulations of bias circuit recovery time                       |

| 4.7  | Single stage of radiation test oscillator                       |

| 5.1  | Interface of the transmitter and receiver                     | 87  |

|------|---------------------------------------------------------------|-----|

| 5.2  | Triplicated transmit and receive units                        | 89  |

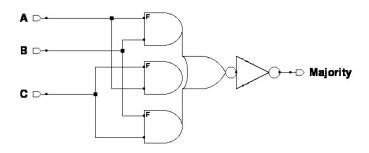

| 5.3  | 2 of 3 voter topology used extensively in this implementation | 90  |

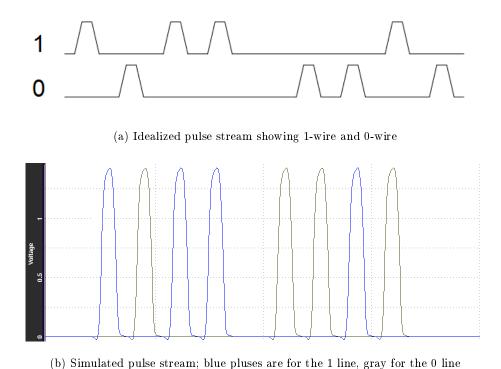

| 5.4  | An example pulse stream                                       | 91  |

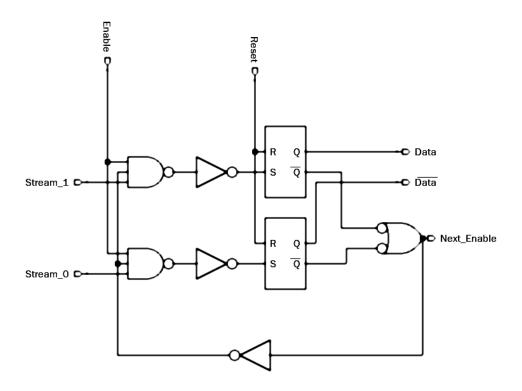

| 5.5  | Single serializer cell                                        | 97  |

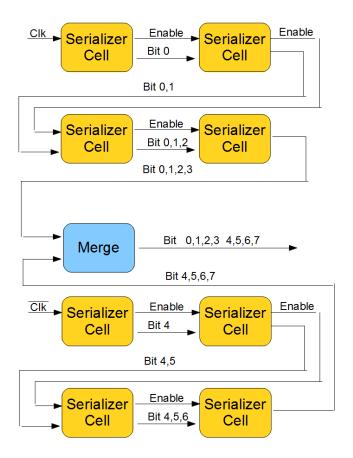

| 5.6  | Serializer architecture                                       | 98  |

| 5.7  | Deserializer cell schematic                                   | 100 |

| 5.8  | Segmented driver schematic                                    | 102 |

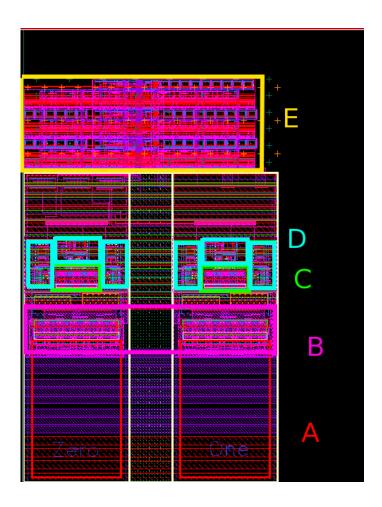

| 5.9  | Transmitter layout                                            | 104 |

| 5.10 | Receiver layout                                               | 105 |

| 6.1  | Radiation sensitive oscillator period VS total dose           | 108 |

| 6.2  | Leakage Current VS Total Dose                                 | 109 |

| 6.3  | Measured output stream                                        | 111 |

| 6.4  | Pulse eye diagram experimentally captured data                | 112 |

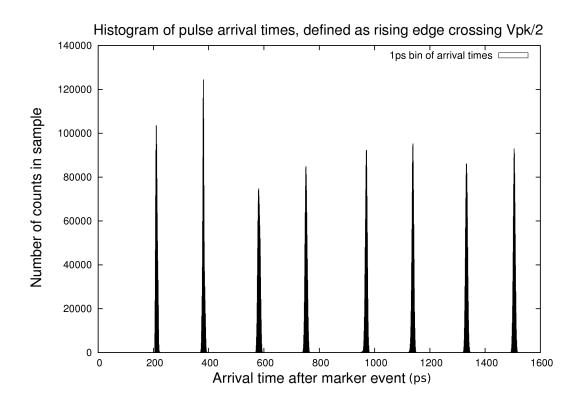

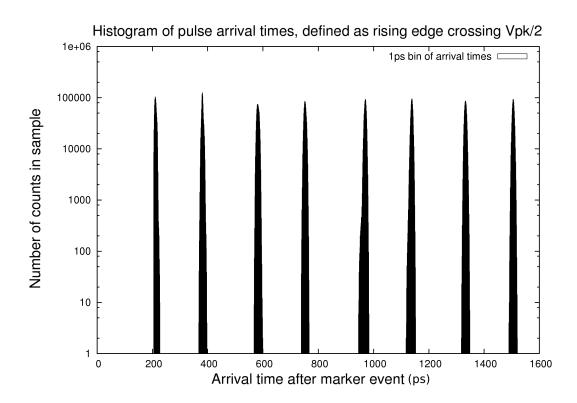

| 6.5  | Arrival time histogram for a full 8-bit word                  | 114 |

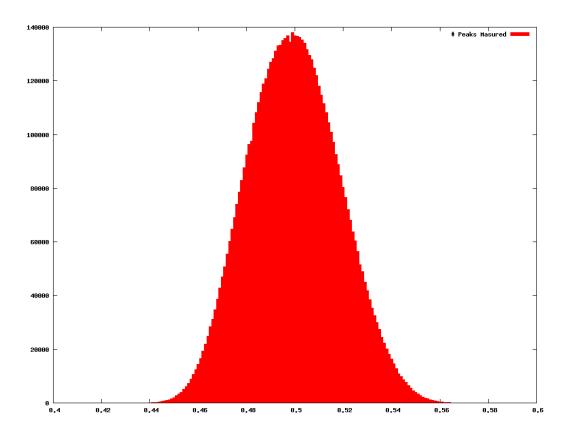

| 6.6  | Distribution of peak pulse voltage                            | 116 |

| 6.7  |                                                               | 117 |

| 6.8  | Pulse to pulse timing                                         | 118 |

| 6.9  | Log scale arrival time plot                                   | 120 |

| 7.1  | Basic Pulse Arbiter and amplifier                             | 123 |

## List of Tables

| 2.1 | Edge vs Pulse propagation time comparison                           | 19  |

|-----|---------------------------------------------------------------------|-----|

| 2.2 | Maximum event rates for alternative signaling methods on a 5mm wire | 23  |

| 2.3 | Performance Estimates for 4-bit SER/DES system                      | 46  |

| 3.1 | Table of solve times for different models                           | 63  |

| 3.2 | Minimum pulse voltage to avoid meta-stability                       | 72  |

| 6.1 | Test bench cabling                                                  | 115 |

| 6.2 | Count data for the fifth pulse from the 8-pulse histograms          | 119 |

### Chapter 1

## Introduction

This dissertation presents a method of describing, constructing and analyzing fast, practical, circuits for communication systems. The motivating application of the developed techniques and circuits is serial communication streams used in the instrumentation of high-energy physics detectors – one of the highest radiation environments where micro-electronics are operated. Radiation environments are a unique application due to radiation induced soft-error. Large physics experiments are additionally a unique application due to a high demand for data. Data links in high energy physics must also consume as little power and chip area as is practical to ease integration. Asynchronous pulse mode circuits and the formal design style demonstrated herein allow efficient construction of a high performance, low power, communication scheme tailored for such extreme environments.

Pulse-mode asynchronous circuits operate without a clock, instead using brief pulses to mark time within a construction. A brief pulse is a useful marker of an event, since there is little uncertainty in the time it marks; this uncertainty is bounded by its duration. This limited ambiguity in pulse arrival can be used to create circuits where uncertainty in time is one of the

major limiting factors for system performance. The nominal pulse width of gates within a pulse circuit becomes a quanta of time upon which the circuit operates. This version of asynchronous pulse circuits does not provide delay insensitive operation, instead, sections of circuitry operate without stage-to-stage feedback in feed-forward mode. The lack of feedback enables potentially faster operations for communications circuits, but comes with two additional costs: the need for timing verification to confirm correct operation, as well as a higher-level description of a protocol that will prevent faster circuits from outstripping the capacity of slower ones.

Described here is a class of asynchronous pulse circuits, deliberately limited to ease analysis and practical construction complexity. A formal method for describing this class of circuits is presented, including a means of verifying correct latch function via a series of timing checks. A method of examining gate behavior by translating the problem into one of Boolean satisfiability (SAT), and thereby avoiding exhaustive simulation is presented. This is followed by an analysis of an example cell set for asynchronous pulse logic. Finally an example of a 5Gbps serial link that utilizes the asynchronous pulse technology and is specifically hardened to radiation will be described.

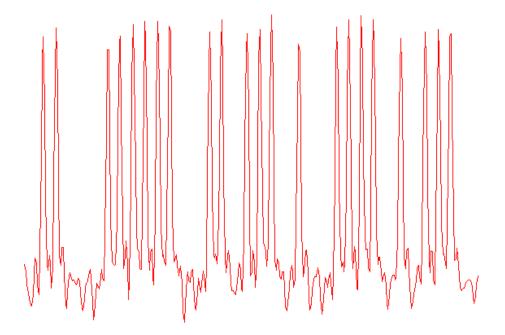

Figure 1.1 is an asynchronous pulse stream. The pulses in this figure mark the occurrence of an event, This dissertation will present a means of generating systems that can use such pulse streams as a core means of operating.

#### 1.1 Asynchronous Pulse Logic

There are many styles of circuit design that utilize pulses. Some of the most famous of these are SRCMOS[1, 2], a clocked logic family, and the asP\*[3], GasP[4], and single track

Figure 1.1: An asynchronous pulse stream. Pulses such as these drive asynchronous pulse gates and are the markers of time in pulse logic. The pulses are of uniform shape, yet the spacing (relative timing) of pulses can vary as long as there is a minimum space.

asynchronous[5] styles of asynchronous circuitry. The prime unique feature of the design style discussed here is that it is both asynchronous and feed forward, that is it neither uses a clock to create timing within the construction, nor does it use a handshake between data source and data sink to regulate the motion of data. This work is also distinct from the feed-forward method of surfing[6, 7], which uses a timing signal much like a phased clock. This paradigm is unlike hand-shake based construction in that timing analysis and margining is used to set the rate at which the system operates. This means that the time for hand-shake times can be removed from the system specification, a small gain for short-range communications, but more important for the long-range case. The removal of a clock from the construction, on the other hand, allows savings in power and area, as there is limited need for feed-back controlled timing recovery.

This work covers a technology for producing high event-rate digital circuits. This technology uses pulses to indicate events which advance the state of the realized machine. By constraining state advance to the existence of a pulse in the correct circumstances, the technology allows for the construction of circuits without a clock or hand-shake required for operation. This allows the designer the freedom to express systems that are delay insensitive and use a hand-shake, and systems that are synchronized by a single timing source using similar circuits and terminology.

The power of this technology is demonstrated by implementing a self-testing high-rate data link. This data link is specifically designed for use in a very high radiation environment, where low-jitter, low-drift timing information comes at a high cost in terms of power and area. This alternate paradigm of pulsed based signaling places timing information explicitly, rather than implicitly, in the data stream – allowing for simple circuits to perform the duties of clock and data recovery from the serial data stream.

The link is constructed to reduce the presence of high-speed clocks within the system, another source of power dissipation that is difficult to harden against radiation-related upset. Data generators and consumers in a system rarely operate one bit at a time, and the circuit interfaces of LHC<sup>1</sup> front-end chips, one of the target applications, are no exception. The link takes advantage of the fact that it only needs to maintain timing accuracy with a slower, parallel bus. This takes the form of small bursts of operation where timing is derived from an uncalibrated delay-line, and then intermittent small pockets of delay as the link re-synchronizes to the slower system clock. In this way the link can operate its internal interface with a 625MHz clock while providing a 5Gbps serial stream, and since there is no continuous tuning operation running (for a calibrated delay line) or high frequency clock the overall system has numerous savings in power and complexity.

This work will present the technology, a useful means of representing events as pulses and constructing a working system. The description covers the definition of a pulse, pulse detection, pulse circuit construction, formalism in expressing a correct pulse system, considerations in physical realization of a pulse system, and an example demonstration of a system that uses both pulses and a clock to construct a 5Gbps serial link and a random number source that implements a 17bit LFSR fast enough to feed the data link. Additionally a discussion of the considerations of radiation damage in such a circuit will be addressed, and the implementation of radiation hard by design in the technology will be demonstrated

<sup>&</sup>lt;sup>1</sup>The (LHC) Large Hadron Collider is currently (2014) the highest energy, and one of the highest luminosity particle accelerator on Earth - and is the design environment of the described link.

#### 1.2 Philosophy

The core goal of this work is to ease the process of correct-by-construction design of practical high-speed circuits. While somewhat nebulous, the term practical high-speed circuit is taken to be a circuit where data rate is of key concern, but trade-offs must be made to meet other system requirements and goals. In the case of the radiation data link, the other goals sought are reductions in power, layout area, and designer effort. Power and area concerns are met by banishing high-speed clocks from the design style, using asynchronous circuits for all high rate interactions. A high-rate high-accuracy clock is deemed too costly for low power and low area efforts.

The effort exerted to specify, construct, and verify a circuit is not frequently touted along with circuits with superlative performance, but is a crucial aspect of design. Simply put, faster design processes allow more options to be considered along the way, and have the chance to provide early feed-back as to the feasibility of implementing new concepts. To this end, formal specification and ease of checking are directly sought as an enabling aspect to the technology.

High radiation environments are studied as an application because they present a unique set of design trade-offs. Device degradation in the face of radiation induced damage is logical concern, with a test-based solution: do not use devices that cannot survive the environment, characterize the parametric drift of devices that are used. Characterization can handle parametric drift, but due to high-energy particle strikes, microelectronic circuits also experience an elevated level of soft-errors; errors in function that can be cleared or corrected. The philosophical approach here is to distribute error detection and correction functionality throughout the circuitry used. Recovery time for a circuit becomes the metric for hardness in this approach,

as during the time period of error, the circuit has lost some measure of correction and is more sensitive to the next error.

#### 1.3 Radiation Hard By Design

Microelectronics are sensitive to ionizing radiation as well as high-energy ions. Radiation effects impact integrated circuits in two basic ways: it can change the properties of the materials that the circuit is made of, as well as depositing charge within the circuit, directly impacting circuit function. This damage manifests it self as both chronic degradation of devices used in circuitry, as well as two acute effects: soft-errors, and hard-errors or device destruction.

Two approaches are used to approach the manufacture of electronics for radiation environments: selection of components for ones that have demonstrated tolerance of radiation environments, and to design systems that have appropriate behavior in the face of radiation even if device failure is a possibility. The whole-system approach involves a designer taking into account radiation effects and adds radiation hardness to the specifications that steer engineering decisions. To achieve a working system considering radiation damage, the devices used may have property drift and intermittent failure in a radiation environment, but if the underlying devices are likely to fail completely, there is little a designer can do to make a working system. Any approach to radiation tolerance must include some work at the device level, but a good system design can extend devices that would other-wise be marginal to be successful components of a fully-functioning system.

The technology described herein was driven by a need for creating data links for sensors at The Large Hadron Collider. The sensors at the LHC produce an exceedingly large amount of

data, and with each upgrade cycle, more and more data becomes part of the design. Sensors in high energy physics are exposed to high radiation levels by design – a sensor that saw no radiation saw nothing in the experiment. Portions of the LHC reach radiation levels that exceed, by many fold, the expected doses seen in space service equipment – a common radiation environment target for micro-electronics. For comparison, many low earth orbit certified components are rated for total dose of 3kGy, while lifetime dose for the highest exposure levels of the LHC are expected to exceed 1MGy - a factor of 300 more lifetime absorbed energy, over a much shorter lifetime.

#### 1.3.1 Options not explored

The application assumes no shielding and no special device-level processing.

Shielding is not a real option for electronics involved in the LHC for two reasons: most important the goal of detecting particles, which would be negatively impacted by shielding, and the second is that at the energy levels of particles of the LHC shielding would be counterproductive. There are two components to this lack of efficacy. First, the very high particle energy means that stopping one particle causes a shower of lower energy particles making the total radiation levels higher. The radiation due to stopping a particle is known as bremsstrahlung. Shielding that would protect against both primary and secondary particles would be impractically thick requiring meters of lead in some cases. The second reason that high energy particles preclude shielding is the notion that particles traveling quickly are unlikely to interact with the material that they are passing through – a concept similar and related to tunneling. There is a peak momentum for absorbed energy for any given particle type – the Bragg peak. Effective

shielding has to reduce the momentum of the particle below this peak, otherwise it is merely increasing the amount of energy deposited in the protected circuit.

There exist microelectronics processes are specially designed for high-radiation environments, yet this work does not require or assume the existence of any special process or device. The rationale behind this decision is multi-faceted. The reasons behind selecting a process tend to center on price and availability. More specialized processes tend to cost more and have the information less-widely distributed. Additionally processes that are less popular have lower guarantee of sustained availability. Making the fewest assumptions about the underlying technology gives a design the best chance to last the test of time and to be broadly used in a collaborative effort, such as in the large experiments at the cutting edge of high energy physics research. The utility of common CMOS processes at the current radiation doses allows their use and hence the benefits in savings and general applicability.

#### 1.3.2 Radiation environment issues in sub-micron CMOS

This work was developed with common planar silicon CMOS processes in the 65nm-250nm process node range. Many of the radiation effects in these processes will be present in other integrated circuit process nodes, and many of the techniques developed to mitigate them will carry forward. For processes in these nodes there is a trend to increased tolerance of total dose in processes with smaller feature size. Starting around the 45nm process node the physical structure of common silicon processes is altered. At the 45nm process node, Intel announced the use of high-k gate material [8], using the heavier-than-silicon metal hafnium in the oxide. Hafnium has a neutron cross section of roughly 100 barns [9], while silicon is only  $\sim$  .7 barns [10]. While the same issues should appear, yet there is the possibility that the dominant damage

mechanisms will change, as is evidenced by the hardness of sub-micron FETs to charge trapping in their gate oxide, a disqualifying issue for higher-voltage FETs with thicker oxide layers.

Current implementations of sub-mircon CMOS processes have a number of similar properties, and, as a whole, are reasonable candidates for radiation hardened electronics. CMOS processes give very high performance field effect transistors, and these processes, highly studied materials are commonly used to construct these field effect transistors. Every device will suffer damage in the face of enough radiation; in the case of field effect transistors the insulating layers are considered the most sensitive to damage. The high dopants densities and thin insulator thicknesses in these processes lead to an attainable level of radiation tolerance. In silicon CMOS processes in the 65nm-250nm scale range  $SiO_2$  is the most common insulator. It is known that silicon dioxide at a thickness of 5 or less it is less susceptible to damage on a per-volume basis[11].  $SiO_2$  Thicknesses in these process nodes is available at thicknesses of 5 or less.

#### 1.3.2.1 Approach To hardening

Radiation environments on the scale being discussed here are harsh on microelectronic devices. The individual components of electronic circuits being constructed are subject to both life-time damage and temporary malfunction. This breaks the mitigation strategy into two fronts: aging effects (changes in behavior on a time-scale much longer than that of the circuit) and soft errors (errant behavior that is on the time-scale of the circuitry involved).

Long term damage sensitivity removes some devices from the realm of practicality, and leads others to require circuits tolerant of their property changes. An easy way to remove the physics from the design equation is to build test structures of all desired devices, and characterize these test structures in the face of radiation. These radiation tests are similar to accelerated

aging tests and are subject to an art and science beyond the scope of this work. The resulting information gathered will be information on lifetime degradation and damage models. Devices that see experience too wide a variation are not used; while devices with some induced damage are used in circuits that have broader tolerance for variation. More adaptive or tolerant circuit designs will always fare better in a radiation environment with regards to total dose since lifetime damage is a form of parametric shift – the more shift tolerated the more damage tolerated.

#### 1.3.2.2 High-power acute issues

There are two classes of acute radiation damage issues: upset and latch-up/burn-out. Latch-up and burn-out are both severe, destructive issues in acute radiation damage. In both cases a particle that strikes the circuit causes an excess of charge in a sensitive region of the struck device. The device is set into a positive feed-back mode where more, rather than less, charge flows through the device; causing a device failure. Latch-up is a potentially destructive condition where an electrical feedback mechanism is triggered. The feed-back path is consists of a parasitic SCR within an integrated circuit[12] that is triggered in to its on condition. In theory latch-up, if caught early, can be stopped prior to device destruction (by powering the device off). Burn-out refers to a similar positive feed-back mechanism, where the critical difference is that the positive feed-back loop includes heating of the device. A radiation strike creates a highly conductive path, which quickly heats, and in the right circumstances, this heating frees carriers making the path more conductive. This means that the mechanism can involve more structures than the SCR, any material that can be coaxed into conduction, has a positive thermal feedback, and is normally operated with a field across it, is potentially vulnerable. When the burn-out

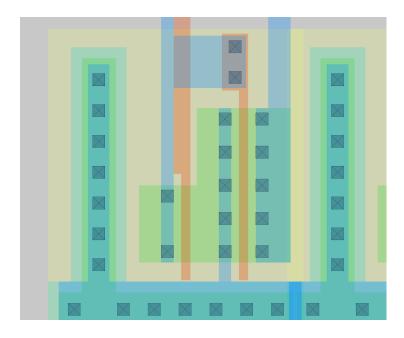

Figure 1.2: Layout of a cell with additional contact regions. Full contact rails surround logic on three sides to help reduce the risk of latch-up.

event includes puncturing the gate oxide of a FET this becomes known as single event gate rupture, a problem most associated with high-power devices[13].

Single event burnout issues are much more common with high-voltage devices[14], and are not expected to be a dominant factor in the systems studied. This leaves latch-up as a key concern for the system. Latch-up issues, being primarily electrical, can be combated by increasing charge collection centers in the layout[15]. To achive this goal dramatically more aggressive a more aggressive than usual substrate and well contact scheme was developed. Figure 1.2 shows a cell with this extra contact layout.

#### 1.3.2.3 Low-power acute issues

Radiation induced charge deposition, so called single-event upset (SEU), is the remaining acute effect of importance. SEU is caused when charge due to a radiation strike merely corrupts information within the integrated circuit. SEU is the largest challenge of deep submicron radiation hard design[16], and the key motivator of the technology developed in this research work. The corruption of information can have a number of impacts from errors in computation to errors in timing and errors in continuous voltages created by bias circuitry. Much of this study will be dedicated to dealing with single event upset.

#### 1.3.2.4 Chronic Issues

There are three key chronic issues due to radiation, both relating to the slow degradation of the materials that make up an integrated circuit. These are total irriadated dose(TID), mostly moderated by photons, lattice damage, mostly moderated by protons and neutrons, and doping inversion, also moderated by heavy particles.

Both TID and doping inversion are limited concerns in deep sub-micron technologies. The primary impact of TID is charge trapping in oxide layers. As already mentioned, the thin oxides common in deep sub-micron technologies have a very low limit to the amount of charge that can be trapped[11]. Because of this hardness, the behavior of thin oxide FETs have been a device of interest and their behavior is well studied [17, 18, 19]. In Effect, wide-channel FETs are radiation hard and suitable for use in the 130nm process[20]. Doping inversion is a damage mechanism where impinging particles change the chemical make-up of the materials in a given silicon wafer. This is a real concern for electronics in the LHC since many such particles are expected to strike electronics within the detector. The high doping levels common to small-scale

planar CMOS technologies offer a good amount of protection against complete type inversion; the doping levels are typically very high in the  $10^{17}/cm^3$  range and greater, while the number of 1MeV  $n^0$  equivalents is limited to  $10^{15}/cm^2$  over the service lifetime. The final issue at hand is lattice damage, cause by collisions between heavy particles and the semi-conductor lattice. Lattice damage reduces the conductivity of field effect transistors, and alters the behavior of bulk devices like bipolar junction transistors and diodes – usually for the worse.

Given the expected chronic issues, Field effect transistors realized in a deep sub-micron process are expected to be much more radiation tolerant than the available alternatives. Thus the decision is made to rely chiefly on FETs as the semiconductor device of choice.

#### 1.4 Permissions and Attributions

The contents of chapter 3 was co-authored with Forrest Brewer and was presented at and published in the proceedings of the 2013 Design Automation & Test in Europe in Grenoble, France conference under the title "Formal verification of analog circuit parameters across variation utilizing SAT" [21]. Additionally the content of chapter 5 was originally presented at the 19th Real Time Conference 2014 in Nara, Japan under the title "5GB/s Radiation Hard Low Power Point to Point Serial Link"; a summery version is in the conference record, and the material in full is currently pending in the Transactions in Nuclear Science edition associated with the conference. This material is used under the terms of the IEEE author re-use policy allowing primary author re-use in subsequent work.

### Chapter 2

## Systematic Asynchronous Design

This Chapter presents a design methodology for creating asynchronous circuits for practical high-performance design; circuits where rate, power, area, and designer effort are all considered for trade-off. The design style works in concert with a logical circuit implementation to enable the description and realization of high-speed asynchronous circuits. The methodology is an adaptation of existing techniques for creating asynchronous, but not delay insensitive circuitry. It is specifically targeted to the production of asynchronous circuits for data link and high-speed communication systems and is an enabling technology for the links developed later in this work.

#### 2.1 Introduction

High-speed link design is a common problem in integrated circuits where interface and communication speeds frequently exceed core clock rates. For example, in the current Intel Xeon E7 lineup no processor has a bus speed less than 6.4GT/s, and no processor has a core

frequency greater than 3.7 GHz[22] and at the opposite end of the power spectrum Atmel offers an 84MHz processor family with USB at 480Mb/s[23]. Complex communication link circuits are found on medium to long wires in integrated circuits, longer PCB traces, and transmission near the dispersion limit for copper cables. These systems involve operating a metal wire near the rate where substantial amplitude loss and symbol timing jitter are serious issues. Correction of signal amplitude is not particularly difficult, however, symbol-dependent timing errors are far more difficult to mitigate.

Synchronous circuits have limited capacity to handle timing issues. Specifically, time domain synchronization is difficult, and is commonly relegated to specialized blocks, such as DLLs, PLLs, and skew compensators, whose behaviors are outside of the synchronous domain. Conventional design methodologies create a complex circuit topology where the link correctness is not guaranteed by the timing closure of the synchronous design. For example, valid sampling of a signal by a deserializer is dependent on the behavior of the associated PLL or timing circuit, not a local property of the deserializer. This issue makes the design of such circuits expensive and complex and slows the adoption of link alternatives because of the perception of risk.

Instead, we implement asynchronous logic blocks to handle the slow parallel to fast serial domain interface. Asynchronous systems are inherently tolerant of timing variance. However, an unconstrained asynchronous design would have potential for high design complexity. Instead, constrained composition rules and a variety of pulse-logic gates are chosen that allow a limited set of classical timing constraints to close both the low-speed and high-speed design behaviors. The high-rate system can then be designed in a coherent manner escaping the complexity of forcing a conventional synchronous timing paradigm to accommodate high variance, high speed signals. Unlike many asynchronous systems, the proposed scheme uses feed-forward

construction. Feed-forward logic design does come at a cost: the timing of the system needs to be verified as part of the construction procedure – system timing is not safe by construction. An important part of the methodology are means to limit the complexity of the timing verification.

#### 2.1.1 Related Work

There are a few asynchronous design paradigms meeting the system rate requirements. At such rates, classical feed-back based delay independent techniques are problematic. In the case of physically long transmission media (starting at the mm scale for multi-GHz signals) time of flight for the electromagnetic wave carrying the signals adds substantially to the system delay, reducing performance. On-die scale structures ( $100\mu$  scale) have substantial propagation delay and at lengths of 1mm has potential signal integrity issues. These considerations defeat design styles based on feed-back such as GasP[4]. Instead, the circuits presented here are a limited sub-class of self-resetting CMOS circuits – a design style that has a reset circuit assigned to small clusters of domino-like logic. SRCMOS circuits work in an inherently pulsed manner. The down side of this is that SRCMOS circuits need pulses to arrive nearly simultaneously for proper function[24]. Work on timing analysis of SRCMOS includes [25, 1]. SRCMOS circuits have seen application in asynchronous circuits in [5, 26] but asynchronous use is commonly restricted to systems that have feed-back to confirm correct behavior.

Pulse reset timing is also noted as reset interference in [5], where the locally reset signal creates a timing constraint in an otherwise timing independent gate.

The notion of using a pulse to synchronize other pulses has been explored in [6] one means of solving the overlap problem of SRCMOS. The implementation comes at the cost of

noise margin due to the conditional lowering of switching thresholds, though conceivably a similar design could be realized that created the necessary timing regime.

#### 2.1.2 This Work

Pulses are used for timing critical communication in a similar fashion to the logic of [24] and [6]. For moving data in situations where the interconnect medium is limiting, especially in terms of jitter, the differences between pulses and edges are minimal, as demonstrated in section 2.2. The logic gates in this work are SRCMOS style gates, with restrictions to simplify analysis. System construction rules partition signals into two classes, to identify signals containing events (e.g. clocks) from others. Static timing verification is then applied relative to system events to confirm correct function. Pulsed signals, with a single characteristic pulse width are used for communicating events in the system. The single pulse-width allows the use of pulse gates, such as in [27, 28, 5, 6] and similar to [4]. These gates are known to maintain a stable pulse width, where logic without feedback would accumulate uncertainty, leading to the eventual decay of short pulses. In the long-range signaling application, high-speed serial streams are assumed to be a pseudo-complimentary pair of wires carrying pulses to mark 1 and 0 bits as events in the bit stream. This encoding creates events for each data bit, simplifying detection and processing of the stream.

### 2.2 On-Chip Signaling: Pulse VS. Edge

A pulse consists of a both a rising and a falling edge and at first glance it would seem that any information carried by a pulse could be done by an edge, with another edge left to spare. Sending information as a pulse has the advantage that a pulse unambiguously marks the

Table 2.1: Propagation times for a slow edge (100ps rise), and a 165ps pulse.

|                | Edge            |               | 165ps I         | Pulse         |

|----------------|-----------------|---------------|-----------------|---------------|

| Coupling noise | Average         | $\sigma$      | Average         | $\sigma$      |

| No coupling    | $251.3 \pm 1.0$ | $8.6 \pm 0.7$ | $239.5 \pm 0.9$ | $7.7 \pm 0.7$ |

| Fastest        | $215.6 \pm 0.9$ | $7.5 \pm 0.7$ | $208.5 \pm 0.8$ | $6.9 \pm 0.5$ |

| Slowest        | $285.9 \pm 1.1$ | $9.5 \pm 0.7$ | $276.7 \pm 1.0$ | $8.7 \pm 0.6$ |

All values shown with 95% confidence interval marked. Both the pulse and edge have similar propagation delay and arrival uncertainty. The pulse width is small to not limit the signaling rate.

arrival of an event while simultaneously allowing consecutive events to have the same transition characteristics. This is in contrast to edge-based signaling, where a rising edge is followed by a falling edge, which usually requires separate detection of rising and falling edges. It has been shown though, that edges can succeed as a marker of events[29].

Because edge-based communication has a theoretical advantage in power and bandwidth, it is important to demonstrate that pulsed signaling does not come at a high cost relative to edges in practical integrated design. A case study using a smaller 130nm process node interconnect wire is used to test this hypothesis. This wire is chosen for two reasons: first, the 130nm node is well characterized, and process variation figures can be produced with confidence; second, it is around this process node where wire dimensions became a limiting factor[30] in signaling rate, making it likely that a similar length wire in finer scale will be implemented in a similar thickness of metal.

#### 2.2.1 Case Study 5mm wire 130nm process node

A 5mm wire in the thin metal layer of a 130nm process node is used as an example to compare pulsed and edge encoding for an event signal. For this metal a conductor thickness of  $.3\mu m$  and a inter-layer dielectric thickness of  $.3\mu m$  is typical. The wire width and spacing is chosen to optimize the cost function of  $delay \times wire\ pitch$  giving a wire width of  $.55\mu$  and a wire spacing of  $.38\mu$ . This configuration gives a fringing capacitance of 100fF/mm, a side coupling capacitance of 31fF/mm, and, assuming a copper conductor, a resistance of  $133\Omega/mm$ . In this process node an inverter with  $1\mu$  wide NMOS, and an appropriately matched PMOS will have roughly  $2k\Omega$  equivalent drive and 5fF of gate capacitance. Additionally such an inverter should have about 5ps of intrinsic delay due to self-loading. Delay optimal sizing [31] of the inverters used for wire repeating gives an inverter size of  $26\mu$  NMOS. With these parameters, minimal worst-case delay (with an even number of stages) occurs with 4 internal repeaters (5 long wire segments) with a 1mm spacing. The single-stage worst-case delay time constant in this configuration is 68.4ps.

#### 2.2.2 Edge-communicated signaling

Arrival jitter is approximated by using Monte-Carlo simulation consisting of 1000 runs, sufficient to gain 95% confidence values for most measures. Process variation is taken from a vendor model for the 130nm process. Power variation is estimated to have a global, correlated variation of 30mV power to ground, modeling power regulator noise. In addition to global power noise, a local, uncorrelated variation of 30mV is added to each power and ground node, modeling IR noise internal to the IC.

When there is a single fast edge (<100ps) of a slow signal (f < 200MHz) the average (across process and voltage variation) propagation time is projected to be  $251.3 \pm 1.0ps$ , close to the value that  $\#stages \times stage \ delay \times ln(\frac{1}{2})$  predicts. The sample standard deviation  $(\sigma)$  of the arrival time in this experiment is  $8.6 \pm .7ps$ . Assuming a Gaussian distribution, a  $5\sigma$  interval gives a delay between 203.5ps to 298.5ps for a 5mm wire, considering only process and voltage variation.

Due to the high coupling capacitance ( 38% of the total) the impact of neighbor wires must be considered. The worst-case jitter occurs when both neighbors are correlated in the same or opposing direction as the main signal. Same direction switching has delay  $215.6 \pm .9ps$  with a sample  $\sigma$  of  $7.5 \pm .7ps$ . The  $5\sigma$  fast arrival time under these circumstances is 173ps. Opposite direction switching delay is  $285.9 \pm 1.1ps$  with  $\sigma \approx 9.5 \pm .7ps$ , giving a  $5\sigma$  slow case of 338ps. This is a range of 165ps of environmental jitter that an ideal latching strategy cannot compensate for. A more common single clock phasing strategy would have a cycle time grater than  $338ps + \tau_{su} + \tau_{clk-Q}$ , approximately 700ps in the 130nm process node yielding a maximum rate of 1.43Gbps.

#### 2.2.3 Pulse-communicated signal

Two features of the above analysis suggest that a narrow pulse might work well. First, the single stage delay for this setup was projected to be roughly 68ps, worst case (5 stages, 338 ps longest projected delay), allowing a pulse on a 70ps time scale. Second, the arrival jitter is 165ps, thus a worst-case environment is unlikely to erase a wider pulse. Table 2.1 compares the propagation times for edges and pulses. Using 165ps as the full-width, half-maximum measure of the pulse, there are no extinguished pulses observed, with propagation times very similar to

edges. The minimum pulse period is twice the pulse width – 330ps, marginally faster than the non-skew-compensated rate of edges; pulses have the potential to operate faster than a clocked edge system.

Using self-resetting gates to create a regenerative buffer, the performance of the pulsed line can be improved. Self-resetting gates protect pulse widths, and thus jitter cannot destroy a pulse, allowing a falling edge closer to the corresponding rising edge. For systems using self-resetting buffers, two conditions must be met: First, the pulse width and its reset time are obeyed. Second, the pulses must arrive in order. The pulse width is set locally within the buffer since it is self-timed. Native pulse width 2.5 in this technology was determined to be 64ps with  $\sigma \approx 4ps$ , giving 84ps for a maximum pulse width, and 168ps for a safe pulse interval. Jitter for the self-timed buffer case is slightly higher than for the inverter buffer case at an estimated total jitter ( $5\sigma$ +pattern dependence) of 188ps. This extra jitter, as compared to the inverter buffer case, is due to the extra logic required in a self resetting buffer. This extra logic also extends the maximum propagation time, in this case it is 405ps. The arrival order uncertainty limit of 188ps is the dominant of the two restrictions.

#### 2.2.4 Pulse vs. edge for marking an event

The study shows the relative propagation timing of pulses and edges are very similar, even when the width of the pulse is small. A key conclusion from this case study is that jitter can dominate gain/bandwidth in limiting performance. A pulse, because it is atomic and unambiguous in its arrival, need not be correlated to any other signal. Thus pulse-based event detection can operate as fast or faster than edge event detection correlated to another signal or state.

Table 2.2: Maximum event rates for alternative signaling methods on a 5mm wire

| Method       | Period | Notes                                 |  |

|--------------|--------|---------------------------------------|--|

| Handshake    | 597p   | Interleaving forward & backward wires |  |

|              |        | (minimizes worst-case propagation)    |  |

| Clocked Edge | 338p   | No Phase compensation                 |  |

| Pulse        | 330p   | Not using self-resetting buffers      |  |

| Edge         |        | Requires DLL/PLL of ~20mW             |  |

| with         | 223p   | (assumes 15ps RMS jitter              |  |

| DLL or PLL   |        | pprox -112dBc/Hz phase noise)         |  |

| Pulse        | 188p   | With self-resetting buffers           |  |

Table 2.2 shows a number of cases, and the associated minimum period of operation for a BER of  $6 \times 10^{-7}$  (corresponding to  $\pm 5\sigma$  variance). For the purposes of comparison, the minimum latch timing is left out of the presented period. In a clocked system, the latch sample interval (setup and hold) would add 50-200ps depending on design style. In asynchronous systems, both pulsed and handshake, latch sampling time does not necessarily add to the minimum period, as both techniques have sampling times built into their respective operating mechanisms. Pulsed communication systems offer a viable alternative to clocked edge systems as shown in Table 2.2. Pulsed systems not only can be faster, but they have the construction simplicity of asynchronous systems, not requiring high-rate, low-jitter clocks.

#### 2.2.5 Long Range Perspective

Data transmission in integrated circuits is a known problem for designers[30] and one of the chief limiters in integrated circuit performance. It is currently common for transmission circuits to be capable of much faster operation that the media that they are connected to, that is to say an inverter with less than 50ps of intrinsic delay may drive a bus with 300ps. When local actions can happen much faster than longer range actions, more complex designs at the ends of a transmission media become practical.

Some initial examples of using more complex transmission and reception logic to combat media limitations came with inter-chip interconnect, leading to the use of pre-emphasis filters such as in [32], but the limitations of slow wires cause the same pattern-dependent problems between circuits whether or not those circuits are part of the same IC chip. Pulsed interconnect offers the chance to solve some these problems.

Pulses can have an intrinsically beneficial frequency spectrum. Return-to-Zero, or RZ modulation is a known method of helping cope with dispersion on long lines, such as fiber optic cables at their upper limit [33]. The signaling method of returning to zero limits the amount of information stored at lower frequencies making dispersion less disruptive to data.

Asynchronous detection, especially the kind that pulses enable, helps with transmission in a lossy media. High data rate signals suffer both attenuation and jitter at the hands of lossy transmission, as demonstrated by the example in section 2.2.4. Signaling techniques that attempt to compensate for some of this effect have been developed but come at a cost in power and complexity [34]. An asynchronous system has the advantage of being able to tolerate timing uncertainty without extra complexity, and thus offers a signaling gain over a synchronous system.

#### 2.3 Composition Rules

This class of systems are not delay insensitive, because it is impractical to have a feed-back path in long-distance communication circuits – that is, it is less costly to design margins to tolerate variance than it is to communicate timing information. The lack of delay insensitivity means timing verification is required for system closure. Static timing analysis is a common part of verifying clocked systems and numerous extensions, such as yield estimation, have been formulated[35]. It is advantageous to use a constraint system that inherits the same analytic methodology, as was done for clocked SRCMOS[1]. The obvious draw-back of an asynchronous, event-driven system is the potential complexity of the set of timing constraints. Described below are a set of constraints targeted directly at providing adequate design flexibility while minimizing the checking and validation complexity.

#### 2.3.1 Terminology

**Data** Signal class that cannot, on its own, cause the system state to change. Communicated by electrical high and low levels.

**Event** Signal class than can, on its own or in conjunction with Data, cause the system state to change. Communicated by short pulses.

Gate A basic unit of system description, either an Event producing P-Gate or a Data-output D-Gate. A gate is triggered by an event dependent on a data condition.

**D-Gate** The gate type with memory. Output signal type is Data.

**P-Gate** The gate type without memory. Output signal type is Event. Implemented in self-resetting logic.

#### 2.3.2 Timing Check Complexity

Static timing for a clocked system involves summing inertial delays along signal paths to constrain each latch-latch path. For acyclic logic, the complexity of the check is simply bound by the number of delays along the path and thus scales as O(n) given n delay bearing nodes including latches. For a circuit with m unconstrained events m! constraints are needed in worst case although this is practically limited by gate fan-in. Unfortunately, behavioral issues such as meta-stability and non-determinism prevent inertial models from applying in any case. In the interest of simplified design effort, we choose to place construction constraints on gates so ensure predictable (inertial) delays apply and have complexity  $O(m^2 \cdot n)$ . This has the consequence that some kinds of circuits cannot be built within these constraints, e.g. fair arbiters, however, all circuits necessary for communication links can easily be constructed.

#### 2.3.3 Logical Restrictions on Construction

Signals are partitioned into two classes or types: Events and Data. The Event class serves to mark time, and is analogous to a clock. The state of a gate can only change with an event. Events are communicated by pulses of finite duration fixed for a system technology. The other class, Data informs state updates in the presence of an event. Data is communicated as traditional digital levels. Correctness for Data signals works as in a clocked system with members of the event class serving as clocks. As usual, the value of a Data signal must be stable between the setup and hold time for each gate relative to the arrival of an updating event.

The second constraint is that a gate may have only one active event at a time. Oneat-a-time events prevent complex timing issues from arising within the relative timing check. In order for two events to be processed simultaneously they must act on separable parts of the system. For two events to inform interacting parts of the system they must have a fixed timing relation ensuring one event at a time. This includes re-timing schemes where such event ordering is enforced. This does place a burden on the designer to describe any two-event behavior as a set of one-at-a-time actions. In this view, arbitration is not a feature of the methodology, instead the designer must describe the arbitration method within the language of the system.

These two rules create a paradigm where timing verification can can happen in  $O(m^2n)$  time complexity, involving two different timing checks limited by this complexity class. Data timing is checked on  $Event \to Data \to Event$  sequences, similar to a clocked system where the sequence is  $Clock \to Data \to Clock$ . Since events are one-at-a-time, a single event sponsors the data change, and a single event causes the result to be sampled. All data transitions are checked between any pair of events giving a check that is square in the number of events and linear in the number of gates in the data path.

#### 2.3.4 Event timing

A known problem for SRCMOS pulse logic is the relative timing of rising and falling edges within the system so that pulses can appropriately overlap[1]. The one-at-a-time pulse model makes the event timing check the dual of the SRCMOS timing check. Here pulses must not overlap for correct behavior. Having a single characteristic time of the event class simplifies the computation, and using as small of a pulse as practical maximizes the systems event handling, either in rate, or in tolerance to variable timing. The event timing model is created with the

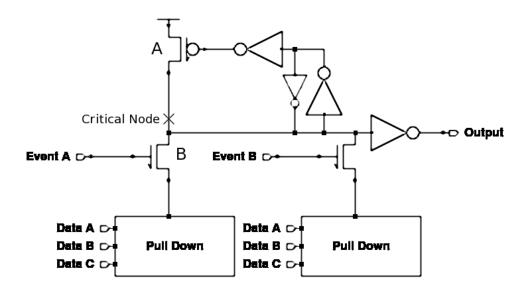

electrical realization of D-Gates and P-Gates in mind. Section 2.5 describes the transistor level design. Conditional Events are implemented with a self-resetting gate structure (P-Gates), while memory is stored in set-reset latches (D-Gate). In both cases, the pulse arriving at the gate serves, effectively, as the sampling aperture for the pull-down network; this sets the data hold window to the actual pulse width of an event. The actual minimum value will be set by the need to reliably sample, and thus by the maximum complexity in the pull-down network. Figure 2.6 shows an Event timing diagram for a D-Gate, marked with some of the critical timing considerations.

A special case requires the pulse width to be part of the timing check. For circuits where the output of a latch is logically feed-back into its input, the input pulse width and the latch delay must be timed such that the pulse-to-Q time of the latch exceeds exceeds the input pulse width. This ensures that a transiting output does not corrupt its own input signals.

### 2.4 System Description

To limit ambiguity, we use a simple formalism to describe an asynchronous pulse circuit. The formalism and use is similar to a guarded action language [36, 37], as the actions of gates are undertaken only when the required event occurs and the pre-conditions are satisfied. The linguistic form allows non-deterministic and parallel behavior, enabling checking that does not explicitly consider execution order. The designer is responsible for creating a system that functions correctly given this order independence.

#### 2.4.1 Language

For simplicity, discussion of behavior will take the form of:

$$Event(guard) \rightarrow action$$

D-Gates have both set and reset behaviors denoted:

$$Data = \begin{cases} Event(guard) \rightarrow Set \\ Event(guard) \rightarrow Reset \end{cases}$$

P-Gates can be triggered by more than one Event(guard) in the case of combination this will be denoted:

$$\left. \begin{array}{c} Event(guard) \\ Event(guard) \end{array} \right\}

ightarrow Event$$

#### 2.4.2 Control Data Flow Graph

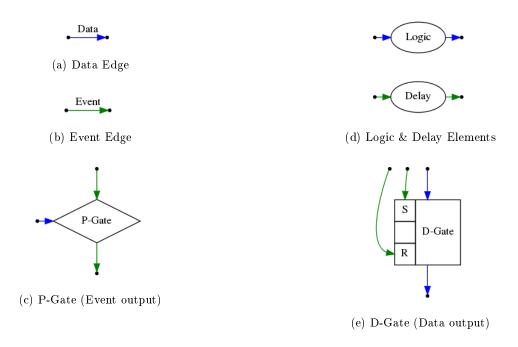

A control data flow graph is a useful structure for visualizing the Event/Data motion within the system. Figure 2.1 shows the basic elements of such a graph: Data and Event edges, D-Gate, P-Gates, Logic and Delays.

#### 2.4.3 3-bit Counter Example

To demonstrate the system we formulate a 3-bit binary counter with asynchronous reset. The counter can be fully described in its latch behavior since there are no conditional events:

$$Bit0 = \left\{ egin{array}{c} Count(\overline{Bit0})

ightarrow set \\ Count(Bit0) \\ Reset \end{array}

ight\}

ightarrow reset$$

Figure 2.1: Control Data Flow Graph elements for pulse logic analysis

$$Bit1 = \left\{ \begin{array}{c} Count(\overline{Bit1} \wedge Bit0) \rightarrow set \\ \\ Count(Bit1 \wedge Bit0) \\ \\ Reset \end{array} \right\} \rightarrow reset \\ \\ Bit2 = \left\{ \begin{array}{c} Count(\overline{Bit2} \wedge Bit1 \wedge Bit0) \rightarrow set \\ \\ Count(Bit2 \wedge Bit1 \wedge Bit0) \\ \\ \\ Reset \end{array} \right\} \rightarrow reset \\ \\ Reset \end{array}$$

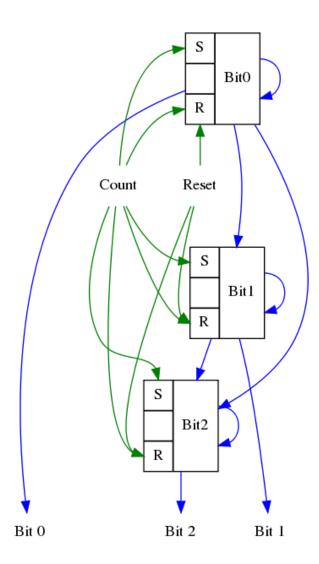

The CDFG for this system is shown in Figure 2.2.

If we choose to construct the system with gated events, there is the opportunity to simplify the design, at the cost of a more complex timing verification. A description of such a system is:

Figure 2.2: 3-bit counter without gated events. Simple structure compared to alternative

Figure 2.3: 3-bit counter with gated events. Higher levels of design re-use, and uses faster gates with fewer and terms in their pull-down networks

$$Bit0 = \begin{cases} Count(\overline{Bit0}) \rightarrow set \\ Count(Bit0) \end{cases} \rightarrow reset$$

$$Count(Bit0) \rightarrow C1$$

$$Count(\overline{Bit0}) \rightarrow Done$$

$$\begin{cases} C1(\overline{Bit1}) \rightarrow set \\ C1(Bit1) \end{cases} \rightarrow reset$$

$$Reset \end{cases} \rightarrow reset$$

$$C1(Bit1) \rightarrow C2$$

$$C1(\overline{Bit1}) \rightarrow Done$$

$$\begin{cases} C2(\overline{Bit2}) \rightarrow set \\ Reset \end{cases} \rightarrow reset$$

$$Reset \end{cases} \rightarrow reset$$

$$Reset \Rightarrow reset$$

This system is equivalent to chaining toggle latches to handle the task of counting, and like a series of chained toggle flip-flops, the timing signal is a derived waveform, rather than a phase of the clock, requiring extra verification steps to confirm functionality. In the first case, Reset must not be concurrent with count. In the second case, Reset must not be concurrent with three different signals (Count, C1, C2), and the timing of data is now dependent on multiple signals, creating a timing uncertainty from a static timing analysis point of view, i.e. without knowing the state of Bits 1, 2, and 3 there are a number of different possibilities of when it is safe to reference Bits 1, 2, or 3 as compared to Count. In true fashion for a functioning asynchronous system, though, a done signal can be produced that reliably indicates an appropriate time to sample the output. This is the CDFG for this alternate realization is in Figure 2.3.

#### 2.5 Gate construction

The strong typing of signals not only simplifies timing checks, it allows the construction of timed gates using pull-down networks. This structure allows a gate to act on a given event given a set of guards, allowing delay tolerant operation. Because the pull-down network can be complex, logic functions are incorporated into the front-ends of D-Gates and P-Gates, giving fast, small designs.

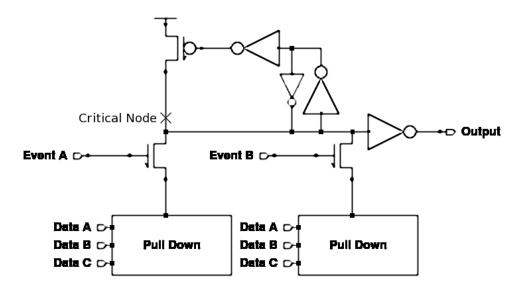

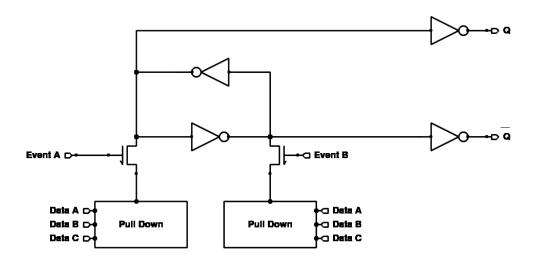

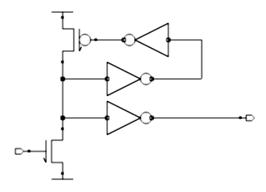

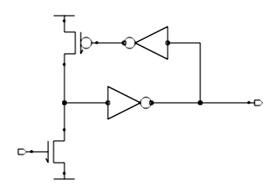

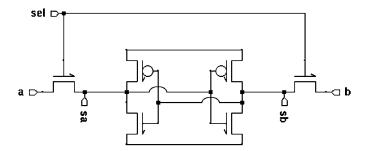

There are two classes of gate in this construction paradigm, pulse *P-Gates* and *D-Gates*. P-Gates, Fig 2.4, have a pulsed output, and thus are used for conditional Events, while D-Gates, Fig. 2.5, have a level output, and are used for Data signals. P-Gates use a local self-resetting logic, and hence are related to the self-resetting logic families.

#### 2.5.1 Pull-down network timing

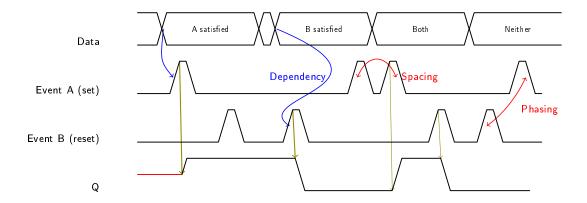

The structure of the pull-down network, combined with the typing rules for Events and Data, create a timing constraint set for each pull-down network. The behavior of these networks are similar for pulse gates and latches, and the analysis holds for both. Correct functioning of the pull-down network determines the values for the timing constraints in the composition rules (section 2.3). The prohibition on event overlapping (the phasing constraint in Fig. 2.6) ensures that the action due to any event is not preempted by another event, a critical requirement for timing verification to not be forced to check event combinations.

Consider the timing of a D-Gate, like the one shown in figure 2.5. Event A triggers setting this latch, while event B triggers reset. In both cases, the action is contingent on the logic of Data A, B, and C encoded into the respective pull-down networks. A timing diagram

Figure 2.4: Drawing of a P-Gate. This class of gate has a pulse as an output, and thus is used for gating events in the system. This gate class would perform the miltiplex and de-multiplex operations in a SER/DES in a high-rate signaling system

Figure 2.5: Drawing of a D-Gate for this technology. This gate has data as the output, and two different input behaviors (a set condition and a reset condition). If a D-Gate has the same event for both set and reset, and complimentary trigger conditions it can behave exactly like a pulse-triggered D flip-flop.

Figure 2.6: Timing Diagram for the SR latch of Fig. 2.5. Critical timing relationships are shown, including: (Olive)Event->Data causal relationships, (Red) relative event timing both same event timing and event-to-event phasing, and (Blue) Data, Event relationships for action enabling.

for this latch is shown in figure 2.6. Electrically, the pull-down network is assumed conducting or non-conducting when the associated event pulse arrives. In the case of the D-Gate, the set condition must be stable for the set pulse and the reset condition must be stable for the reset pulse.

The pull-down network impacts the timing equation in two ways: intrinsic delay, and its impact on pulse timing. First is the intrinsic delay, the amount of time for the switch between conduction and non-conduction. Static timing analysis avoids the state of the system, thus all of the turn-on and turn-off combinations will be converted to minimum and maximum propagation times. Typically the turn-on time associated with the pull-down network very limited, for example the pull-down net for the set pull down network for the first 3 bit counter from Section 2.4.3 has an estimated intrinsic delay range of up to 20ps in the  $130\mu$  process, less than the transition time of signals in the system. The second impact the pull-down network impacts timing is by limiting current through the pulse signal's transistor. In the case of the 3-transistor pull-down from the  $3^{rd}$  bit of the counter the expected source degeneration of the pulse transistor is  $\frac{1.5k\Omega\cdot\mu}{width}$  to  $\frac{3.k\Omega\cdot\mu}{width}$  in the same process.

#### 2.5.2 Pulse timing

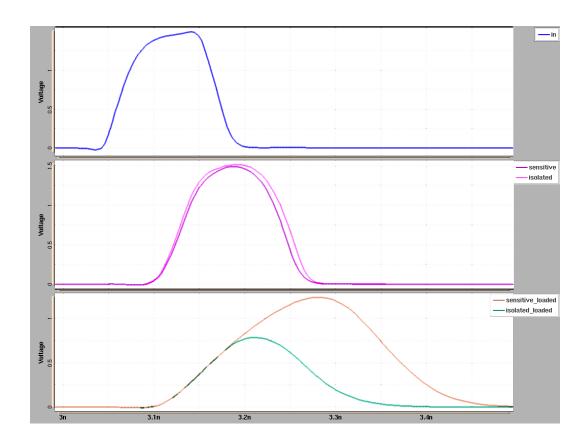

Pulse width is a critical property for correct gate operation; too narrow a width and the gate will not reliably function, too long a pulse and performance is compromised. Both D-Gate and P-Gates have similar pull-down behavior, and a study of minimum width can be done with either. P-Gates are the only type that produces pulses and thus set the functional pulse width in the system.

Correct P-Gate behavior requires that input pulses are capable of triggering the P-Gate. A P-Gate is considered triggered when it's critical node, marked in Figure 2.4, is pulled down during an active event. Phrased in another way, the total charge that flows through the pull-down network during a pulse must be sufficient to overcome the keeper and flip the critical node. The keeper circuit will establish a minimum voltage required to start removing charge from the critical node, creating a threshold below which any signal in the event line is ignored. This will be the minimum input voltage  $V_{Imin}$ . The strength of the Event input is characterized by its transconductance,  $g_m$ . This transconductance takes into account the size of the associated transistor, the effects of the resistance in the pull-down network it is attached to, and the effects of the keeper circuit. The value of  $g_m$  should be selected to be valid over the range of inputs between  $V_{Imin}$  and  $V_{DD}$ . Given  $g_m$  the triggering condition is:

$$\int_{pulse} gm \cdot min(0, V_{in}(t) - V_{Imin}) \ge V_{DD} \cdot C_{crit}$$

Where  $V_{in}(t)$  is the input waveform and  $C_{crit}$  is the critical node capacitance. This equation gives us an important property of pulse detection: a lack of pulse amplitude can be corrected with a longer duration pulse – the area between the pulse and the minimum input threshold is the key property that indicates detectability; this property is illustrated in Figure 2.7. For long range communication, issues of attenuation can be off-set by increasing pulse duration. In the case of lossy wires, increasing pulse width also reduces attenuation, thus increasing pulse width is doubly effective.

In the case of the  $3^{rd}$  bit of the 3 bit counter, the  $g_m$  is approximated to be:  $\frac{170\mu A}{\mu m \cdot V}$  on average giving a input threshold voltage calculated to match at 300mV. This means that, with

Figure 2.7: Two pulses of different volatage and duration demonstrating similar detectability.

Pulse voltage directly impacts detectability, which determines the required minimum pulse width for a functioning system

(a) Load isolated feed-back network. Preferred design for maximum rate, low-load situations

(b) Load sensitive feed-back system. More robust to high-load situations; helps protect against unexpected pulse attenuation

Figure 2.8: Two self-reset feed-back network options.

this setup, for every fF of  $C_{crit}$ roughly  $9ps \cdot V$  of pulse area is needed to trigger the system using  $1\mu$  wide transistors in the pull-down network.

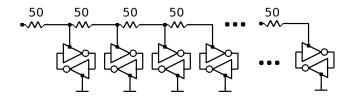

#### 2.5.3 Drive and Feed-back network

The characteristic pulse width of a self-resetting gate is set by the propagation delay through the feedback path. The output amplitude is dependent on both the output driver and its load. Pulse detection requires that the delay of the feedback path must match or exceed the amount prescribed by driver and load environment.

The feed-back network for a pulse gate can be connected or, alternately, isolated from its load environment, as shown in Figure 2.8. The load isolated model (Figure 2.8a) can be faster than the load sensitive feedback and has more reliable timing, as it does not have a longer interconnect impinging on feed-back. This feed-back network is well suited for situations where the loading is either constant and known, so that a correct pulse width can be selected, or

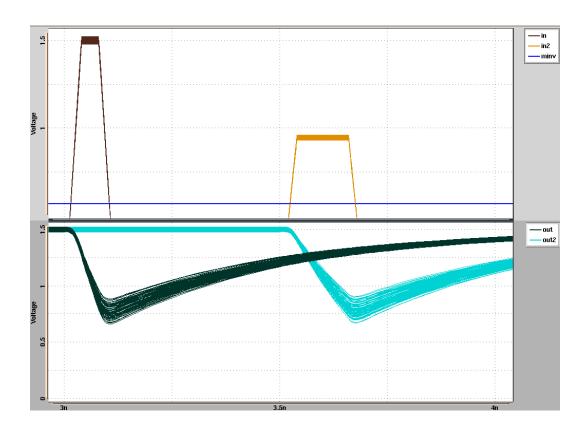

for small fan-out situations where pulse attenuation is unlikely and speed and repeatability are more important. Load sensitive feedback (Figure 2.8b) on the other hand can be useful in a production environment where cell design and cell use are not concurrent. The load sensitive gate is slowed by placing it in a high-load environment. This is undesirable from a performance perspective, but by slowing the feed-back loop, the circuit can improves detectability and thus reduces the odds of a unexpectedly high load causing pulse attenuation. Figure 2.9 shows a comparison of the isolated feedback system to the sensitive feedback system. In the lightly loaded case, with  $7fF/\mu_{driver}$  of load capacitance the two feedback networks perform similarly. In the heavily loaded case, with  $50fF/\mu_{driver}$  of load, the sensitive feedback produces a slower, more detectable result than the isolated feedback. If speed is more critical than detection, the isolated network is nearly 200ps faster in this example. If detection is more critical, the sensitive feedback has roughly 4 times the detectability in the heavily loaded case.

#### 2.6 Data Link Performance Estimation