### UNIVERSITY OF CALIFORNIA Santa Barbara

## Abusing Hardware Race Conditions for High Throughput Energy Efficient Computation

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Advait Madhavan

Committee in Charge:

Professor Dmitri Strukov, Chair Professor Tim Sherwood Professor Luke Theogarajan Professor Forrest Brewer

December 2016

The Dissertation of Advait Madhavan is approved:

Professor Tim Sherwood

Professor Luke Theogarajan

Professor Forrest Brewer

Professor Dmitri Strukov, Committee Chairperson

September 2016

### Abusing Hardware Race Conditions for High Throughput Energy Efficient

Computation

Copyright © 2016

by

Advait Madhavan

To my Parents.

### Acknowledgements

My learning experience at UCSB would not have been as enjoyable or insightful without the help of a lot of people around me. Therefore, I acknowledge them for their contributions, not only to the work presented in this dissertation but also my individual growth.

Firstly, I would like to thank my advisor, Prof. Dmitri Strukov for giving me the opportunity to be a part of the incredibly diverse research environment at UCSB and Strukov group. I would specifically like to thank him for discussing a variety of brilliant ideas with me as well as providing an environment of freedom and support. I was allowed to make mistakes, direct my research along my personal scientific interests and was provided a safety net, all for which I am very grateful.

I would also like to express my gratitude towards my committee members, with whom I was lucky to have many direct interactions resulting from classes to research. Prof Luke Theogarajan's circuit classes were very insightful and inspirational and he himself has been a constant source of scientific and psychological support for me. I am grateful to have been treated so warmly by him and his group which has allowed me to be part of more than one research environment at once. Prof. Tim Sherwood's computer architecture class at UCSB was probably one of the best classes I every took. I have learnt so much from Prof Tim, from making convincing arguments, breaking down problems effectively, to maintaining a healthy relationship between graduate school and life. Prof. Forrest Brewer's advanced VLSI and chip design classes were the first tape-outs that I was involved in. Since those classes in the early years of graduate school, Prof. Brewer has been a constant source of ideas and I am grateful to have been exposed to the tremendous breadth and depth of his knowledge.

I would also like to thank my fellow lab-mates with whom I spent a lot of time getting my hands dirty. In spite of being in different groups, Melika Payvand and I were lucky to work on multiple collaborative chip design projects together. We spent a lot of late nights in the lab doing chip tape-out work which led to the growth of a beautiful friendship and I am very grateful to her for that. I admire her for the dedication and care with which she approached surroundings and I hope for some of that to be rubbed off onto me as well. I thank members of Luke's group (Luis, Mohamed, Aaron, Jennifer, Melika, Danielle) who made the 4110 a very lively place to work. Also, I would like to thank Mirko, Farnood, Bhaswar, Xinjie and Michael with whom I have had countless discussions regarding research and who have directly helped me with my work.

I am grateful to friends of mine from high school(Karun, Ishaan, Aneesh, Apoorv, Ghodu, Aditi) for always encouraging me and keeping my spirits up

when I talk to them and visit them. My roommates (Geetak, Sagar, Nitin, Arvind (RIP), Gina, Chirag, Urmish, Manik, Ravi, Dinesh, Abhinav, Sanmay) and friends (Bugra, Mike Gama, Nikita, Billy) in SB over the years have been great to live with and have truly made these years at UCSB truly memorable. I would also like to thank my parents(Madhavan Kutty and Sreedharan Sudha) and my grandparents (P S Nayar and Vasini Nayar) for creating an environment of learning in the house as well as my sister for all the bickering and squabbling we went through. Gopal, Shanta, Siddharth and Kunal will always be a part of my family and I am eternally grateful for the boundless support that I have received from them. Last but not the least, I would like to thank Tanya Das, who has been with me through thick and thin for the last four years, has been a constant source of love and kindness and has taught me many valuable life lessons. I could not have done it without her. I would like to thank you all for your efforts.

## Curriculum Vitæ

### Advait Madhavan

#### Education

Ph.D., Electrical and Computer Engineering, University of California, Santa Barbara, 2016

M.S., Electrical and Computer Engineering, University of California, Santa Barbara, 2014

B.Tech, Instrumentation and Control Engineering, Netaji Subhas Institute of Technology, New Delhi, India, 2010.

### Publications

- •A. Madhavan, T. Sherwood, and D.B. Strukov, Race logic: A hardware acceleration fordynamic programming algorithms, in: Proc. ISCA14, Twin Cities, MN, June 2014, pp.517-528.

- •A. Madhavan ,T. Sherwood, and D.B. Strukov, Abusing Hardware Race Conditions todo Useful Computation, Micro Top Picks, Special Edition, June 2015.

- •A. Madhavan, T. Sherwood, and D.B. Strukov. Energy efficient computation with asynchronous races Proceedings of the 53rd Design Automation Conference (DAC) June 2016. Austin, TX.

- •A. Madhavan, G. Adam, L. Gao, and D. B. Strukov, Analog and digital computing withmemristive devices, extended abstract in: Nature Conference on Frontiers in ElectronicMaterials: Correlation Effects and Memristive Phenomena, Aachen, Germany, June 2012

- •A. Madhavan and D.B. Strukov, Mapping image and network processing tasks ontohigh-throughput CMOL FPGA circuits, in: Proceedings of VLSI-SoC12, Santa Cruz, CA,Oct. 2012.

- •Melika Payvand, Advait Madhavan, Miguel Angel Lastras-Montao, Amirali Ghofrani, JustinRofeh, Kwang-Ting Cheng, Dmitri Strukov, Luke Theogarajan, A Configurable CMOS MemoryPlatform for 3D- Integrated Memristors. Proceedings of ISCAS 2015.

- •Justin Rofeh, Avantika Sodhi, Melika Payvand, Miguel Angel Lastras-Monao, AmiraliGhofrani, Advait Madhavan, Sukru Yemenicioglu, Kwang-Ting Cheng and Luke Theogarajan, Vertical Integration of Memristors onto Foundry CMOS Dies using Wafer-Scale Integration, Proceedings of the ECTC 2015.

### Abstract

## Abusing Hardware Race Conditions for High Throughput Energy Efficient Computation

#### Advait Madhavan

We propose a novel computing approach, called Race Logic, which utilizes a new data representation to accelerate a broad class of optimization problems, such as those solved by dynamic programming algorithms. The core idea of Race Logic is to deliberately engineer race conditions in a circuit to perform useful computation. In Race Logic, information, instead of being represented as logic levels (as is done in conventional logic), is represented as a timing delay. Computations can then be performed by observing the relative propagation times of signals injected into a configurable circuit (i.e. the outcome of races through the circuit).

In this dissertation I will introduce race condition based computation and talk about multiple VLSI implementations. We first begin by considering a synchronous approach, which uses simple clocked delay elements. Though this synchronous implementation outperforms highly optimized conventional implementations of the well-studied, DNA sequence alignment problem, its third order energy scaling with problem size and limited dynamic range of timing delays are its major pitfalls. Next, in the search for energy efficiency, we study asynchronous designs in order to understand the performance trade-offs and applicability of this new architecture. Finally, I will present the results of a prototype asynchronous Race Logic chip and demonstrate that Race-Based computations can align up to 10 million 50 symbol long DNA sequences per second, about 2-3 orders of magnitude faster than the state of the art general purpose computing systems.

# Contents

| List of Figures |                                  |                                           | xii |  |  |

|-----------------|----------------------------------|-------------------------------------------|-----|--|--|

| 1               | Intr                             | oduction                                  | 1   |  |  |

| <b>2</b>        | Bac                              | kground and General themes                | 8   |  |  |

|                 | 2.1                              | Half a century long Exponential           | 8   |  |  |

|                 | 2.2                              | Approaches to Energy Efficiency           | 14  |  |  |

|                 | 2.3                              | The Role of Approximations                | 17  |  |  |

| 3               | Race Logic and Application Study |                                           |     |  |  |

|                 | 3.1                              | Hardware Implementations                  | 23  |  |  |

|                 | 3.2                              | Sequence Alignment                        | 29  |  |  |

|                 | 3.3                              | Sequence Alignment as a Kernel            | 39  |  |  |

| 4               | Race Logic and Application Study |                                           |     |  |  |

|                 | 4.1                              | Analytical Estimates and Results          | 51  |  |  |

|                 | 4.2                              | Energy Optimized Architecture             | 56  |  |  |

|                 | 4.3                              | Generalized Synchronous Race Architecture | 60  |  |  |

|                 | 4.4                              | Discussion and Conclusions                | 64  |  |  |

| <b>5</b>        | Asy                              | nchronous Race Logic                      | 69  |  |  |

|                 | 5.1                              | Delay element and Current source          | 73  |  |  |

|                 | 5.2                              | Top level Architecture                    | 78  |  |  |

|                 | 5.3                              | Results and Discussion                    | 81  |  |  |

|                 |                                  | 5.3.1 Simulation Results                  | 82  |  |  |

|                 |                                  | 5.3.2 Variation Analysis                  | 87  |  |  |

|                 | 5.4                              | Conclusion                                | 90  |  |  |

| 6 | Chip Design and Testing |                                |     |  |

|---|-------------------------|--------------------------------|-----|--|

|   | 6.1                     | Objectives                     | 92  |  |

|   | 6.2                     | Architecture and Test Plan     | 94  |  |

|   |                         | 6.2.1 Input/Output Circuitry   | 96  |  |

|   |                         | 6.2.2 Array and Bias Circuitry | 99  |  |

|   |                         | 6.2.3 Clock and Control Logic  | 105 |  |

|   | 6.3                     | Results                        | 107 |  |

| 7 | Sun                     | amary and Conclusion 1         | 10  |  |

# List of Figures

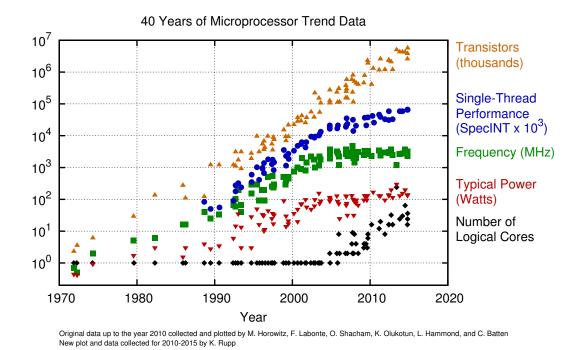

| <ul><li>2.1 Microprocessor trend data over the last 40 years</li></ul>                                                                     | 9  |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

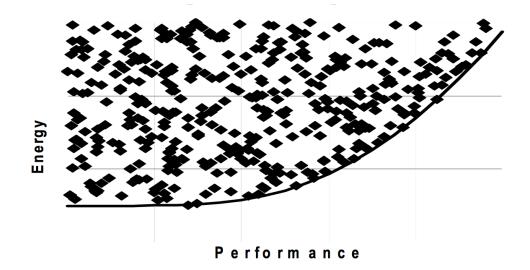

| that would provide high performance at very low energy cost.[16]                                                                           | 15 |

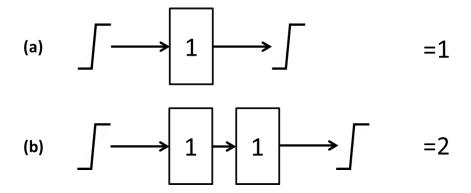

| 3.1 Delay domain representation. (a) Unit delay element that delays                                                                        |    |

| input rising edge by 1 "unit" time step, (b) stacking two delay elements                                                                   | 01 |

| one after another performs addition operation                                                                                              | 21 |

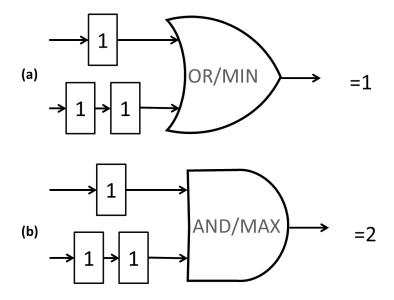

| 3.2 Delay domain computation. (a) Using an OR gate to implement<br>MIN function by selecting a first arriving of multiple edges, (b) Using |    |

| an AND gate to implement MAX function by selecting a last arriving                                                                         |    |

| of multiple edges.                                                                                                                         | 22 |

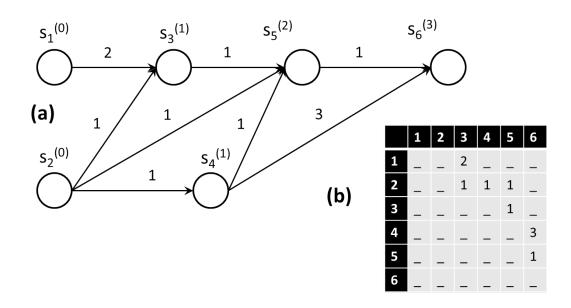

| 3.3 Toy DAG problem: (a) Directed acyclic graph with numbered                                                                              |    |

| nodes and edges. The superscript denotes the linearization index of                                                                        |    |

| each node while the subscript denotes the node number. (b) Equiva-                                                                         |    |

| lent scoring function that shows the edge weights $(W_{ij})$ , i being the first                                                           |    |

| column and j being the first row) connecting the nodes in tabular form.                                                                    | 24 |

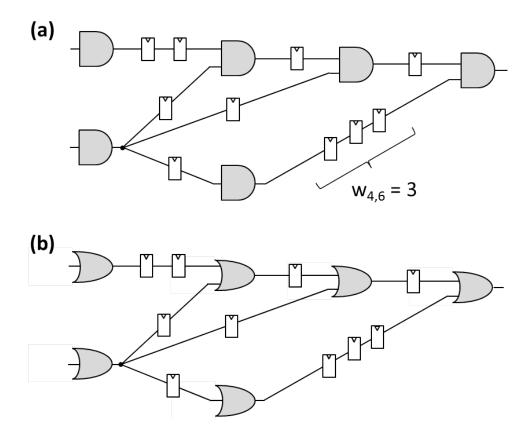

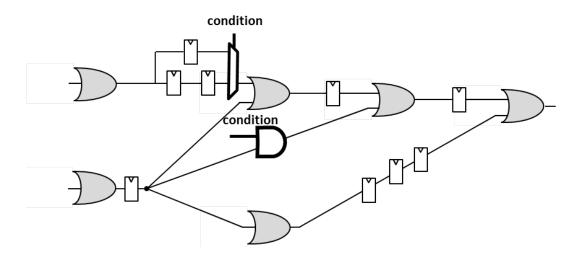

| 3.4 Race formulation: (a) Longest path AND race formulation achieved                                                                       |    |

| by replacing edges with flip flops and nodes with AND gates. (b) Dual                                                                      |    |

| shortest path OR race formulation.                                                                                                         | 26 |

| 3.5 Race formulation: (a) Longest path AND race formulation achieved                                                                       |    |

| by replacing edges with flip flops and nodes with AND gates. (b) Dual                                                                      |    |

| shortest path OR race formulation.                                                                                                         | 28 |

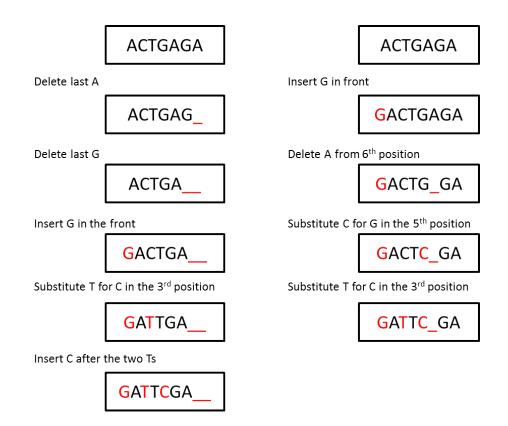

| 3.6 Edit operations: Multiple different ways in which simple edit op-                                                                      |    |

| erations such as insert delete and substitute can be used to convert toy                                                                   |    |

| DNA sequence $P = ACTGAGA$ " to $Q = GATTCGA$                                                                                              | 32 |

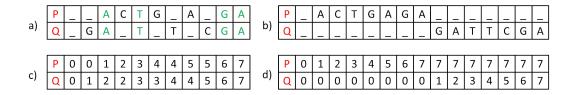

| <ul> <li>3.7 Alternate alignment representations: panels (a) and (b) show two different methods of aligning the sequences P and Q from figure 3.6.</li> <li>Panels (c) and (d) are the respective alignment matrices</li></ul>                                                                                                                                                                                                                                                | 33       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| and (b) respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34       |

| shown in panel (b) and (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35       |

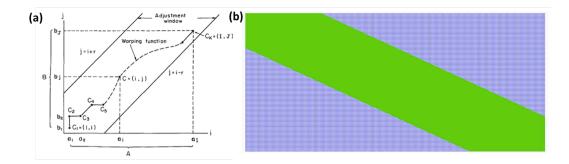

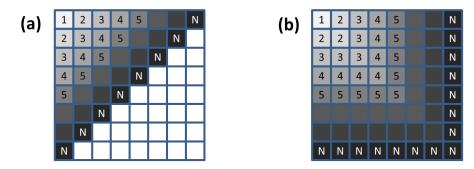

| the Sakoe-Chiba band that limits the warping score                                                                                                                                                                                                                                                                                                                                                                                                                            | 40       |

| [35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43       |

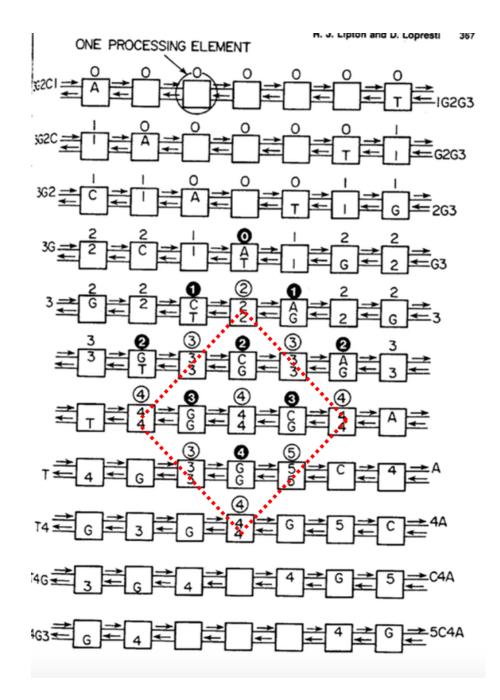

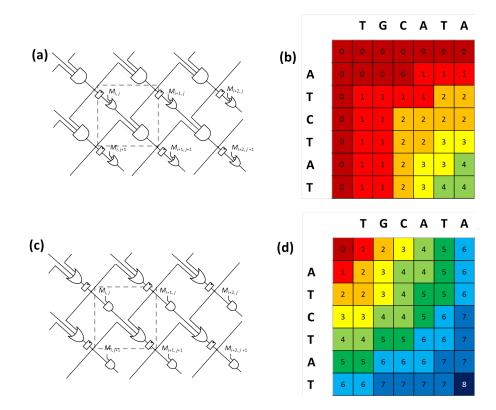

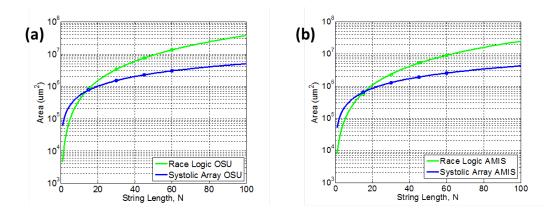

| <ul> <li>4.1 Original figure from the Lipton and Lopresti systolic engine.[24]</li> <li>4.2 Race logic implementation of sequence alignment. Panels (a) and (c) show the circuit level diagrams for Race implementation (AND and OR) of score matrices from 3.9(a,c). Panels (b),(d) show the propagation of the race wavefront at each clock cycle until it reaches the output.</li> <li>4.3 Area scaling with respect to problem size for multiple standard cell</li> </ul> | 48<br>49 |

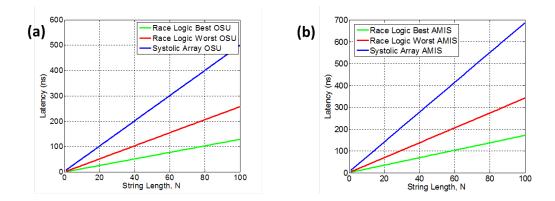

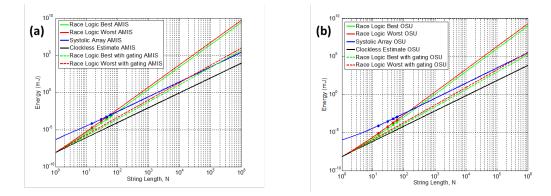

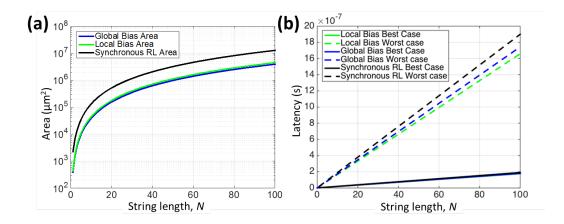

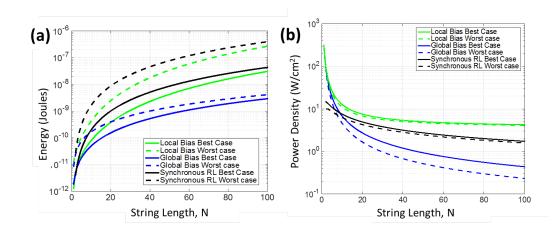

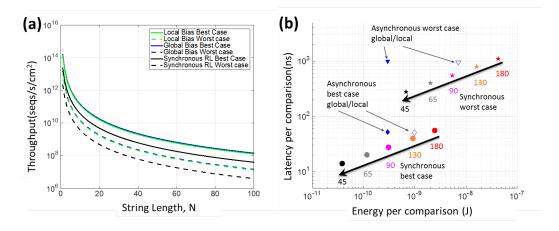

| sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52       |

| <ul> <li>architecture.</li> <li>4.5 Latency with respect to problem size for multiple standard cell sets</li> <li>4.6 Throughput with respect to problem size for multiple standard cell</li> </ul>                                                                                                                                                                                                                                                                           | 52<br>53 |

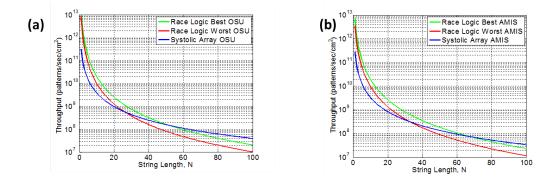

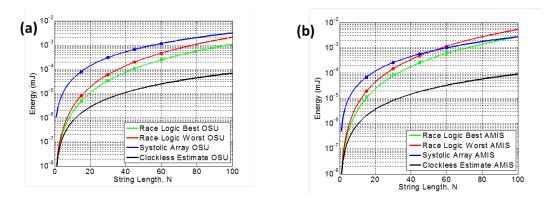

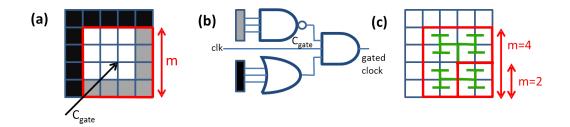

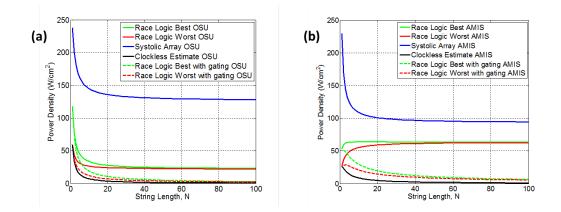

| <ul> <li>sets</li> <li>4.7 Energy with respect to problem size for multiple standard cell sets</li> <li>4.8 Clock gating: (a) granularity of the clock gating cell, pictorial representation of parameter m (b) clk gating circuitry (c) htree fabric and</li> </ul>                                                                                                                                                                                                          | 53<br>55 |

| multiple clock gating granularities                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57       |

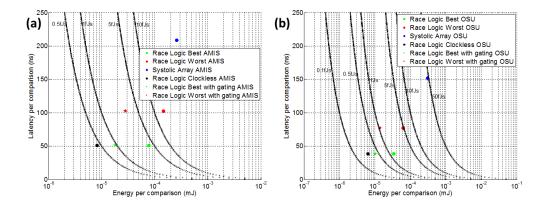

| clock gating for multiple standard cell sets.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59       |

| <ul> <li>4.10 Clock gating power density: power savings before and after clock gating for multiple standard cell sets.</li> <li>4.11 Pareto plots comparing Race Logic with systolic implementations for array size N= 30, across different standard cell sets.</li> <li>4.12 Block Substitution matrix or BLOSUM62.</li> <li>4.13 Generalized race logic architecture which allows a larger symbol space and high dynamic range compared to the implementation previously discussed</li> </ul>                        | 60<br>61<br>62<br>63 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

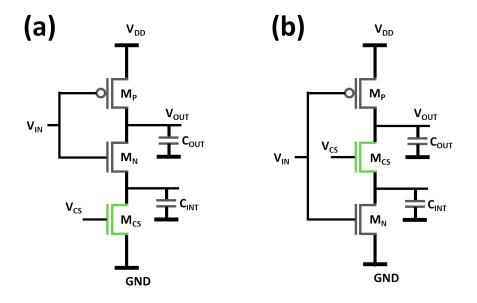

| 5.1 Delay element choices are based on the location of the current con-<br>trol transistor. (a) shows the current control at the tail of the switching<br>transistor $M_N$ whereas in panel (b) the current control splits the output<br>node                                                                                                                                                                                                                                                                          | 75                   |

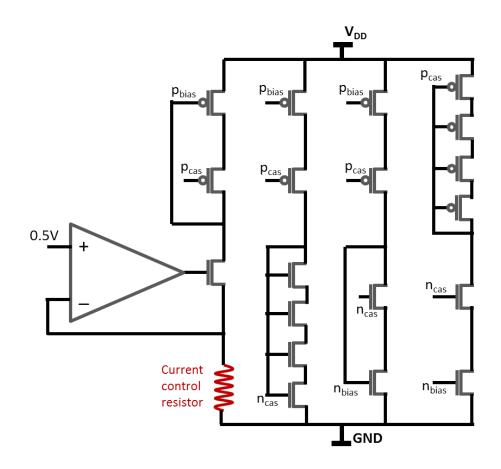

| 5.2 Current source design: The current source works by pinning 500mV across a resistor that is variable and externally controllable, using a high gain op-amp. The current that is generated is largely independent of                                                                                                                                                                                                                                                                                                 |                      |

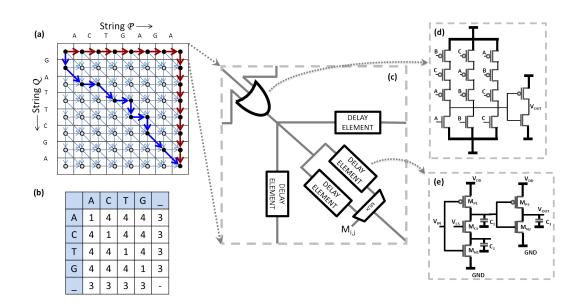

| process or supply variations. This current is then mirrored to generate<br>bias and cascode voltages to be distributed to the rest of the array<br>5.3 Top Level Architecture: Panel (a) shows the Edit Graph used in<br>the previous chapter and (b) shows a more commonly used score ma-<br>trix in DNA sequence alignment. Panel (c) shows the unit cell of the<br>asynchronous Race Logic architecture. It is similar to the synchronous<br>approach in many ways, but differs in the design of the delay elements | 77                   |

| and the OR gate as shown in panels (e) and (d) respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80                   |

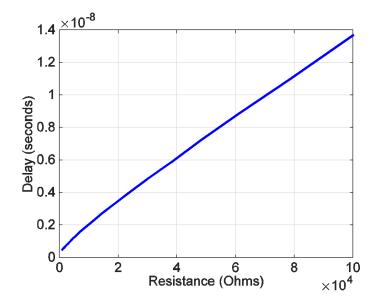

| 5.4 Variation of Delay with Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                   |

| the same                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83                   |

| Bias asynchronous cases. (b) shows the power density for the same 5.7 Simulation Results: Panel (a) shows the throughput of the Synchronous Race Logic implementation and the Local Bias and Global                                                                                                                                                                                                                                                                                                                    | 85                   |

| Bias asynchronous cases. (b) shows the power density for the same.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                   |

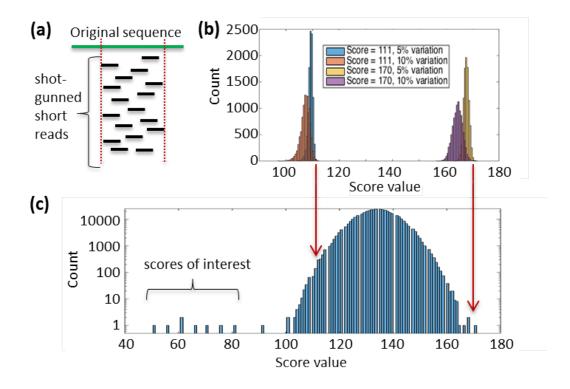

5.8 Preliminary variation study: (a) A cartoon of shotgun sequencing process, (b) Monte Carlo simulations (10,000 runs) of the alignment scores for two particular pairs of DNA strings for the OR-type Race Logic with variation-prone delay elements, and (c) representative score statistics in human genome shotgun sequencing. The reference DNA strings is the same in both panels (b) and (c). The query strings used in panel (b) were chosen such that their alignment scores with the reference DNA string correspond to the start and very end of the hump in the score distribution, which is highlighted with red arrows. (The simulation results show that the distributions on both panels are rather insensitive to the particular choice of DNA strings.

88

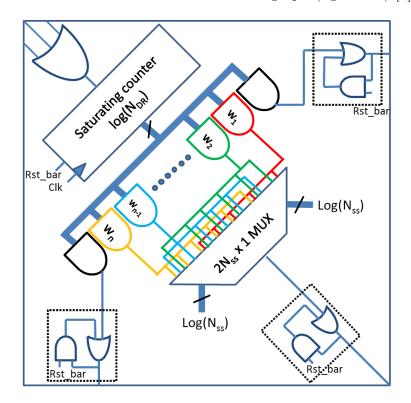

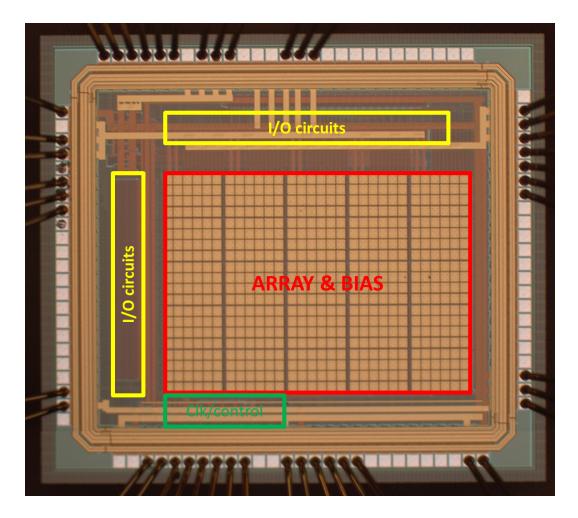

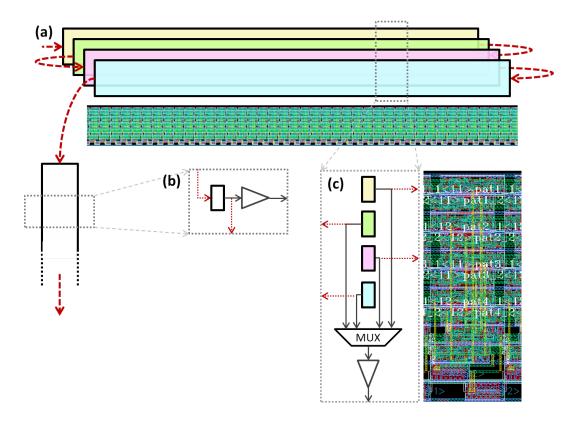

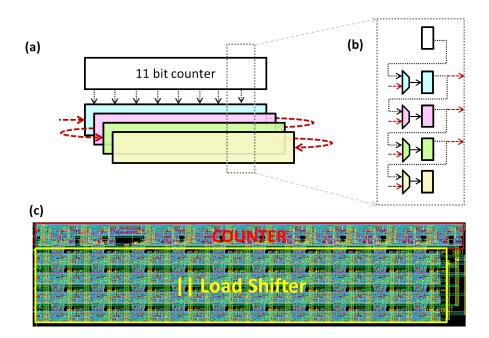

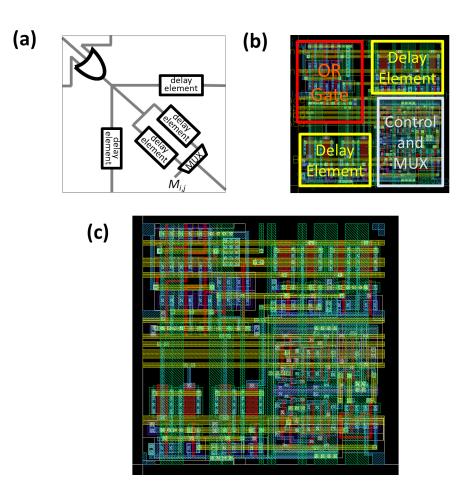

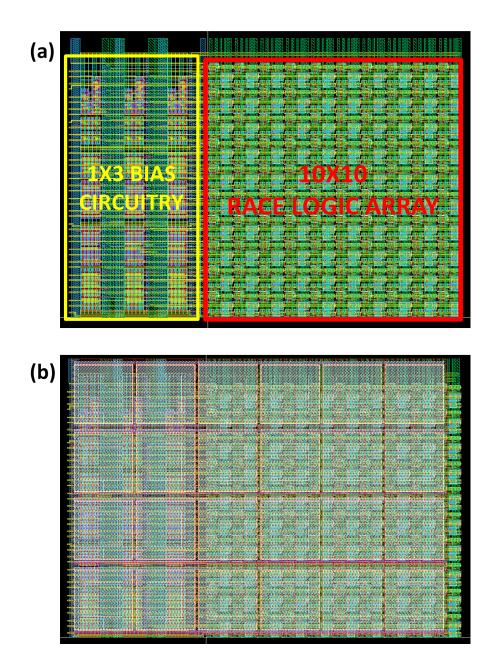

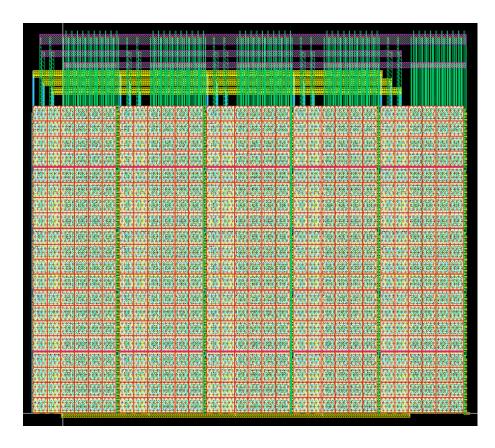

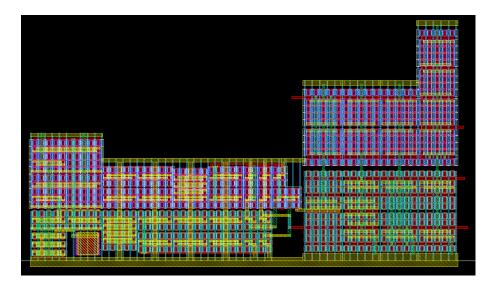

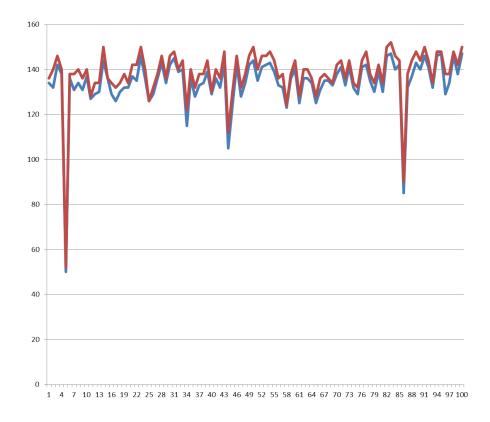

6.1shows the micrograph of a fabricated chip with architectural block 97Shift in circuit and Scan chain: Panel (a) shows the overall 50X4 6.2shift registers scan chained to store four patterns (P1 to P4) extending into the Q pattern. (b) shows the details of the single Q bit element while (c) shows the details of the P bits and how different 50 long sequences are buffered into the Race Array 986.3 Counter circuit and shifter register output: Panel (a) shows the overall 11 bit counter parallel loading in to the first shift register while (b) shows the details of how the counter values are parallel loaded into each shift register for one MUX configuration and to a scan chain shift register for another. (c) Shows the layout of the blocks from (a) and (b) 1006.4 Race Logic cell: Panel (a) shows a simplified circuit of the Race Logic cell while (b) shows the layout of the panel (a). Panel (c) shows a detailed version of (b) to accentuate the tiling structure. It can be seen that the corners are designed to lock into each other and allow diagonal connections while bias nodes go across the cell while power runs from top to bottom. 1016.5 Race Logic Array: Panel (a) shows a 10X10 Race Logic array with the relevant local bias circuitry without metal layers 4, 5 and 6. On careful inspection, the tiles nature of this granularity is also visible. (b) shows the same layout with MIM Caps on top of the array in the top 3 metal layers. 103Race Logic Array: 50 X 50 RAce logic array complete with bas 6.6 circuits and MIM capacitors. 105Tunable current source for current biasing using off chip resistors. 1066.7

6.8 Simulation vs Real data with the blue line representing simulated value and red line representing real data. The x axis represents different sequence alignments while the y axis represents the score. . . . . . . . 108

## Chapter 1

# Introduction

The seemingly insatiable advancement in technology over the last half a century has had a significant and wide ranging impact on society and has ushered in, what is called by sociologists, the "information age". Named rightly so, our ability to store and manipulate information has followed more or less a steady exponential over the last five to six decades. To get a feeling of the enormity of this progress, a short comparison between representative examples is in order. The ENIAC (Electronic Numerical Integrator and Computer)[6] is considered as the first electronic general purpose computer and was designed in the 1940's primarily to calculate artillery firing tables for the US Army, Ballistic Research Laboratory. It could perform 60-second trajectory calculations in 30 seconds, what would usually take a skilled person with a desk calculator about 20 hours. It consisted of  $\approx 100\,000$  components, primarily resistors, vacuum tubes, capacitors and relays, and had a machine cycle of 200 microseconds, allowing it to compute 5000 additions, 357 multiplications and 38 divisions a second. It took up a total floorspace of  $167m^2$ , weighed 30 tons, consumed 180kW of power and cost half a million dollars. Today, the iPhone6 uses a 64bit Cortex A8 ARM chip which is composed of  $\approx 1.6$  billion transistors. It operates at a frequency of 1.4GHz and can process approximately 1.2 instructions per cycle in one of its 2 cores, which amounts to 3.36 billion instructions per second. The power consumption of this chip is around 2.3W with a footprint of  $89mm^2$  and the entire 700 dollar phone weighs in at 129 grams. Trillions of dollars and countless man-hours of research, development and production have allowed information storage and processing to move beyond its initial military and aerospace applications and become ubiquitous in the world today. From massive datacenters that host the internet to household appliances, smart-phones, automotive applications, and with the upcoming surge of the Internet of Things (IoT), the estimated number of devices that are powered by silicon hardware is estimated to reach 50 billion by the year 2020.

In spite of this continued proliferation of silicon computing for a host of everyday applications, silicon itself is facing some major, potentially industry changing, challenges. For many years, consistent improvement in Complimentary Metal Oxide Semiconductor (CMOS) processing technology fuelled large increases in processor performance and throughput. Predominantly, improvements in lithography based techniques allowed engineers to build transistors with smaller feature sizes each advancing process generation. Known colloquially as Moore's Law, what this meant was, for the same chip area, computer architects had an exponentially larger number transistors to work with, each with exponentially higher energy efficiency. The results of this can be seen in a modern microprocessor that is a highly complex piece of machinery, generally consisting of multiple cores with each core employing sophisticated mechanisms to improve performance.

However, in recent years, the law of diminishing returns seems to be catching up. As of 2016, 10nm devices are still under commercial development with industry leaders such as Intel and TSMC announcing production and commercial release to start in early 2017. Development of 7nm and 5nm nodes have also been projected by the year 2021. The 5nm node was assumed to be the end of Moore's law as quantum effects such as tunneling would cause gate leakage to go beyond permissible limits and hence significantly reduce yield. As the increase in the number of transistors that can be put on a chip seems to be slowing down, powering them efficiently is already a much more immediate concern. Leakage currents have begun to consume a significantly larger portion of the power budget than before, hence pushing CMOS scaling out of its traditional regime. As a result, after the 130-90nm technology node, though transistor areas continue to shrink, their switching energy no longer declines. Moreover, practical concerns such as thermal management (cooling) and battery life keep the power budget fixed. Therefore, with each new technology node, the number of transistors that can be switched simultaneously is exponentially decreasing.

This energy problem that is being faced by computing, in literature, is known by multiple monikers. The growing divide between available transistors vs utilizable transistors has caused researchers to dub this the *utilization wall* [46]. Other terms such as Dark/Dim silicon refer to the underutilized transistors that have to be turned off or under-clocked to maintain fixed power budgets [12]. Dark Silicon and the Utilization wall that causes it have caused architects to shift their focus from designing the highest performance circuits, as these are almost guaranteed to exceed the power budget. Instead, as power and energy become more expensive relative to chip area, newer architectures will have to focus on spending chip area to buy energy efficiency, which opens the door to specialization and heterogeneity. Researchers have predicted that future chips are going to be populated by a large number of application specific hardware accelerators that are going to be used only part of the time. This is already being implemented in cellphones where multiple digital functions have been integrated on one chip, each having its own dedicated processing hardware. In this dissertation we propose a novel computing approach, called Race Logic, which utilizes a new data representation to accelerate a broad class of optimization problems, such as those solved by dynamic programming algorithms. The core idea of Race Logic is to deliberately engineer race conditions in a circuit to perform useful computation. Information, instead of being represented as logic levels as is done in conventional logic, is represented as a timing delay. Computations can then be performed by observing the relative propagation times of signals injected into a configurable circuit (i.e. the outcome of races through the circuit). The main advantage of this novel approach is that the set of arithmetic and logical operations that can be most efficiently expressed changes, leading to new tradeoffs and architectures. Through the manipulation of the natural delay chaining inherent to digital designs, the basic operations of MIN, MAX, and ADD-BY-CONSTANT can be implemented in a way that results in superior latency and energy efficiency for certain classes of problems.

We will begin this dissertation by exploring some general themes and approaches to energy efficiency at both architecture and circuit levels as obtained from literature. Starting with a more detailed study of the scaling laws that give rise to the Utilization Wall, we will discuss performance vs energy trade-offs, digital vs analog design trade-offs, as well as the role of approximations in improving energy efficiency of computing systems. These general themes will be detailed in Chapter 2 and employed in the understanding of Race Logic by comparing it to other architectures.

Chapter 3 introduces Race Logic and using a very simple example, elaborates on various implementation methods. It also introduces an important application, the DNA sequence alignment problem that is used as a toy problem in the rest of this thesis.

Chapter 4 performs a case study utilizing the DNA sequence alignment algorithm. It first introduces a traditional systolic array method of performing such a computation and then presents a synchronous Race Formulation with the interest of comparison between them. A more general and energy efficient implementation of Race Logic is also presented.

Chapter 5 addresses some of the drawbacks of synchronous Race Logic, especially in terms of energy efficiency. It pushes for improving energy efficiency by removing the clock which translates to using asynchronous delay elements that are less power hungry but also more prone to variations. In this chapter we also perform a variation analysis to look at how process variations at the delay element level affect the functional correctness of the architecture and what the demands of the architecture are. Chapter 6 presents the architectural, circuit level and floor-planning decisions that went into designing a Race Logic chip. We also present layout level details with die photographs and chip results.

Chapter 7 presents a summary and discussion of this work, and future directions that can be taken.

## Chapter 2

## **Background and General themes**

### 2.1 Half a century long Exponential

Among the many innovations that have enabled the technology revolution, lithography of silicon has been a significant one. One can say that at the centre of the steady increase of performance per watt per unit area, has been the battle against physical laws and variations to constantly improve fabrication techniques and enable scaling of silicon. Figure 2.1 plots CPU data over the last forty years and shows the impact of scaling on important performance parameters [7]. At first glance one can see that the number of transistors integrated on a single chip has been the only metric that has seen a steady exponential rise over the last four decades. Though yield and chip area were a concern in the early years, our ability to power these transistors effectively and extract as much performance as possible continues to be a challenge that will shape the course of the semiconductor industry today.

Figure 2.1: Microprocessor trend data over the last 40 years

The predominant VLSI technology in the early years from 1971-81 was based on PMOS or NMOS technology with depletion mode loads. The earliest chips of this era include Intel's and history's first fully integrated microprocessor, the Intel 4004, which ran at a clock speed of 740kHz and could perform addition of two 8bit numbers in about  $850\mu$ s. Successors of 4004 include the 8080, which extended the 4bit word size to 8bits and upgraded the clock speed to 2MHz, and the famous 8086, a 16bit microprocessor which pushed clock speeds to 10MHz. To be compatible with the then prevalent TTL technology, the supply voltage was kept at a constant 5V while the minimum feature size scaled down from  $10\mu$ m to about  $1\mu$ m. As a result, the saturation current didn't scale effectively, causing power dissipation to grow enormously, affected by commensurate increases in chip area, complexity and operating frequency. This first power crisis caused a shift from NMOS to CMOS designs which cut down large leakage transients, hence reducing power dissipation by an order of magnitude. The power savings thus gained from switching to CMOS was large enough to keep the supply voltage  $(V_{dd})$  constant for almost another decade.

In 1974, Robert Dennard explored different methods of scaling CMOS devices and suggested a "constant field" scaling method in which the voltage levels were also scaled with lithographic dimensions [8]. He pointed out that this would allow power density to remain a constant, as the reduction in energy per switching event, due to lower supply voltage, would exactly match the increase in the number of transistors, as both obeyed square law behaviour. By the mid-nineties, as transistors began to scale into the sub-micron regime, still with a 5 volt  $V_{dd}$ , internal device electric fields grew to large values and pushed Dennard scaling into effect.  $V'_{dds}$  have systematically scaled down by roughly  $10V/\mu m$  with each successive generation from  $0.5\mu$ m down to 130nm. In spite of this improved Dennard scaling, power dissipation increased by almost 50X from the early nineties to the mid two thousands, as shown in figure 2.1. This was predominantly as a result of various architecture and circuit design optimizations such as deeper pipelines, better sizing of gates, out of order execution, performance driven architectures and larger chips. During this time frame, processor speed also saw a significant boost with clock frequency almost doubling every few generations, scaling much faster than gate speed, a testament to circuit and architectural innovations of this era. Representative chips of this era include the Intel's Pentium 4, PentiumD, AMD's AthlonXP, Opteron and IBM's PowerPC970, Xenon.

As clock frequency continued to increase, engineers had to face the power wall again. As hobbyists and computer enthusiasts were liquid cooling their overclocked 8 GHz CPUs, the law of diminishing returns showed that boosting clock frequency was not the most effective way of extracting performance per watt. Though it continued to improve single thread performance for many applications, it was seen that energy used to open up data and instruction level dependencies would provide much higher overall performance gains. This slowing down of clock frequency scaling is clearly visible in figure 2.1 and coincides with a single thread performance slowdown and an increase in number of logical cores. This signifies the start of the multicore era where power constraints guided the search for improved performance

|             |                    |                                     | Clas- | Den-  | Le-   |

|-------------|--------------------|-------------------------------------|-------|-------|-------|

| Para-       | Description        | Equation                            | sical | nard  | akage |

| meter       |                    |                                     | Scal- | Scal- | lim-  |

|             |                    |                                     | ing   | ing   | ited  |

| W,L         | width, length      |                                     | 1/S   | 1/S   | 1/S   |

| $t_{ox}$    | oxide thickness    |                                     | 1/S   | 1/S   | 1/S   |

| $V_{dd}$    | supply voltage     |                                     | 1     | 1/S   | 1     |

| $C_{gate}$  | gate capacitance   | $WL/t_{ox}$                         | 1/S   | 1/S   | 1/S   |

| $I_{d,sat}$ | saturation current | $WV_{dd}^2/Lt_{ox}, WV_{dd}/t_{ox}$ | S     | 1/S   | 1     |

| F           | frequency          | $I_{d,sat}/C_{gate}V_{dd}$          | $S^2$ | S     | S     |

| Р           | dynamic power      | $NC_{gate}V_{dd}^2F$                | $S^3$ | 1     | $S^2$ |

**Table 2.1:** Different types of scaling ranked in historical order and their effect on chipparameters. S denotes scaling factor, > 1

by exploiting parallelism. Though out-of-order execution and deep pipelines in single core machines already allowed for effective sharing of resources, multiple simpler cores provide a better energy and price point compared to complex high frequency uni-processors. Representative chips of this era include, Intel Core series (i3,i5,i7), Xeon E7 and AMDs FX Bulldozer.

Unfortunately no exponential can last forever and now engineers have hit a fundamental physical limit which prevents the threshold voltage,  $V_{th}$  from scaling. Since the thermal voltage  $(V_T = kT/q)$  doesn't scale, reducing the threshold voltage causes an exponential increase in leakage current. Leakage current in today's designs is already large enough (approx 40% [47]) that it needs to be accounted for in the power budget and hence,  $V_{th}$  is set as a result of power optimization and not by technology scaling. During the Dennard scaling regime,  $V_{dd}$  scaling was complemented by commensurate lowering of the threshold voltage, but this cannot continue if the scaling is leakage limited as shown in Table 2.1. The dynamic power in this leakage limited regime grows exponentially and hence, due to a fixed power budget, leads to exponential reduction in active switching circuitry each process generation. In a fixed amount of time, there is only a certain amount of energy dissipation that can be tolerated by the cooling system, and with leakage accounting for a size-able portion of that energy, *edges have become expensive*.

Race Logic includes this general purpose computing research wisdom by encoding information in timing delay which in a logic circuit manifests as a single rising edge propagating through a set of spatially laid out parallel paths. Smaller and larger magnitudes can be encoded on the same wire with only a single edge, with the smaller delay encoding smaller magnitudes while a larger magnitude would mean longer delays (or vice versa, based on the kind of encoding). In both cases a single edge on a wire encodes the signal with only the arrival times determining the magnitude which results in less wires (less area and capacitance) and less switching activity (less toggling) compared to traditional approaches. This encoding scheme results in superior energy efficiency, not only as a result of this single edge based temporal coding, but also as a result of the simplicity in performing some operations that this form of coding provides.

### 2.2 Approaches to Energy Efficiency

As the performance per watt metric begins to take a front seat in terms of design constraints in modern systems, a wide variety of options is available. Exploring the design space of circuits or architectures, we see a certain trade-off between energy and performance of designs that informs our choices regarding the desired implementation. This trade-off is shown in Figure 2.2. Interestingly, the qualitative shape of this curve always remains the same for different architectures and circuits and it follows the law of diminishing returns[16].

A first glance analysis of the curve reveals that at low energy points (bottom left region), small changes in energy can lead to large changes in performance, while at high performance regions (top right region), a marginal increase in performance costs a lot of energy. The choice of what implementation is picked depends upon the application and in most cases lies along the pareto frontier. In other words, the energy of the architecture is reduced at the cost of increasing

Figure 2.2: Energy vs Performance design space for a given function. The pareto curve shows the boundary of possible solutions in this space. The most favourable point in this space is the extreme bottom right as that would provide high performance at very low energy cost.[16]

the latency. Similar examples to these are architectures that are partitioned such that specific regions of the architecture are connected to different power supplies and body biases. Timing critical paths are adjusted for performance while other regions are optimized for energy efficiency.[16]

Another subset of techniques have no energy cost for keeping performance fixed. This is generally implemented by reducing the energy that is being wasted by the system. Clock and power gating strategies are good examples of such techniques as they turn off power and clocks to regions of the architecture/system that are not producing useful outputs. The dual of this could thought of as systems that improves performance at no extra energy cost. Exploiting parallelism with multiple functional units would allow each functional unit to be running at a slower rate, instead of just one functional unit running at the maximum rate. For example, due to the shape of the curve shown in figure 2.2, the marginal energy saved by running a functional unit at a half the speed could be used by other another functional unit and would overall achieve the same performance while still keeping the energy within acceptable bounds. This argument is in essence, the logic behind the surge of multi-core architectures.

The best techniques though, are those that improve both energy and performance, hence having negative energy cost for performance improvement[16]. These techniques generally involve problem reformulation, a new information representation, or algorithmic changes that reduce the overall computation that needs to be performed. Most of these methods are highly application specific and require changes at both architectural and implementation levels. Such techniques are generally accompanied by custom hardware that allow orders of magnitudes of energy savings and performance gains. As a simple example, performing multiplication and division operations can be complex and require special hardware for binary encoding schemes, but using logarithmic [45] number systems makes performing such operations as straightforward as addition and subtraction. CORDIC [49] algorithms extend this idea to perform vector rotations in a bit-serial manner by using clever encodings that allow computation for arbitrary angles by using simple iterative shift and add procedures. Many algorithms designed along these lines were conceived at a time when chip area was extremely expensive and performing parallel computation operations such as square root would be prohibitively expensive in area, but it is perhaps worth revisiting these ideas in the new context of power efficiency.

During the course of development of the Race Logic formulation, we have utilized most of the above techniques to shrink the energy-delay product of Race based computations compared to traditional approaches. Firstly (as we will see in chapter 3), as a result of temporal information representation, some arithmetic operations such as MIN, MAX and ADD BY CONSTANT become trivial to implement. The simplicity thus afforded allows for an ease of implementation which results in significant performance gains as compared to standard implementations. Also, as will be presented in more detail in chapter 4, we try to minimize energy consumption in our synchronous Race Logic implementation by employing clock gating strategies.

### 2.3 The Role of Approximations

Another means of reducing power dissipation in computation systems that has come to the fore during recent years, is to trade off functional correctness for energy efficiency. Some methods leverage the error tolerance of the application such as those in domains of image processing, machine learning and computer vision. Though this error tolerance can originate from imperfect human perception, lack of a universal best result, or redundancy in the input, it allows the outputs of these algorithms to be numerically approximate rather than accurate. This relaxation on numerical exactness provides some freedom to carry out imprecise or approximate computation [48]. The freedom for approximation can allow for increased simplicity of designs, which can leave room for architectural and circuit level innovations to boost performance or reduce energy consumption. Some implementations identify functionally non-critical regions of the algorithms and use VOS (voltage overscaling) to save power[29], while other provide VOS cores with a low precision error compensation core[41]. Other methods explicitly target designing imprecise functional units such as adders or multipliers that are optimized for energy efficiency, speed, or wiring delay. Stochastic methods analyse the probabilistic nature of circuit types and design out low probability worst cases which reduce performance[17]. An interesting approach dubbed Razor utilizes this principle in a general purpose computing system by implementing real time error checking using shadow registers and literally runs at the edge of functional correctness[11]. The system then utilizes DVS (Dynamic Voltage Scaling) to reduce the energy dissipated by the system until the system is running on the "razor's edge" of failure.

As we will see in Chapter 5, Race Logic embraces the approximate computing paradigm as we forgo synchronous implementations due to high power dissipation that results from continuous clocking. Since information is encoded in timing delays, moving away from a synchronous domain could result in a significant reduction in noise immunity. We move to an asynchronous approach with analog components which is by nature more prone to process variations, power supply switching variations, and other environmental factors. We perform an error tolerance study on our application space to understand how variations in the timing delay from these aforementioned components affect the functional correctness of the application and show that the performance of the architecture is minimally affected.

The general themes discussed in this chapter lie at the heart of computing and outline different methods, generally used to extract performance and energy efficiency in modern computing systems. Race Logic is no exception. Starting from the information representation that helps preserve edges in an attempt to reduce dynamic power(discussed in chapter 3), to the application variation study (performed in chapter 5), the general themes presented here will be called upon repeatedly to push performance per watt of our designs.

## Chapter 3

# Race Logic and Application Study

Race conditions are notoriously knows for causing errors in software and hardware systems. They occur as a result of the output of a certain block being dependant on the sequence, or the timing of other events in the system. When the designers of such a system are unaware of these timing intricacies, these race conditions manifests as bugs. Hardware race conditions result in hazards or glitches that cause the output of a system to flip once or multiple times but systems such as Karnaugh Maps can be used to identify them before they happen and design them out of the system. Software races on the other hand are trickier to reproduce and debug since they are as a result of relative timing difference between interfering threads. Problems occurring in production systems can therefore disappear when running in debug mode, when additional logging is added, or when attaching a debugger, often referred to as a "Heisenbug".

In this work we propose a method that makes positive use of race conditions. How we plan to do this is by setting up a set of race conditions in a system that are input dependant. A signal navigates these set of race conditions and the path that is taken by this signal (unknown beforehand), solves the problem. The main idea of Race Logic is to encode information in a timing delay. We do this by defining a unit delay element that acts as a fundamental unit of computation as shown in figure 3.1(a). How it functions is by delaying an input transition to its output by 1 unit. Aside from the physical implementation of such a delay element, a few properties remain constant.

Figure 3.1: Delay domain representation. (a) Unit delay element that delays input rising edge by 1 "unit" time step, (b) stacking two delay elements one after another performs addition operation.

One such property is addition; as shown in figure 3.1(b), the simple act of chaining two unit delay elements result in an input transition to be delayed by a value of two unit delays. In this representation a slower delay corresponds to a larger value and a faster delay to a smaller one. MIN and MAX operations can also be implemented trivially with such a delay encoding.

Figure 3.2: Delay domain computation. (a) Using an OR gate to implement MIN function by selecting a first arriving of multiple edges, (b) Using an AND gate to implement MAX function by selecting a last arriving of multiple edges.

In figure 3.2 we see two parallel delay paths each with a different delay. If we trigger rising edges at the inputs of these two parallel paths simultaneously, we see that the first arriving edge is going to be the one with MIN delay while the one arriving later will the MAX of the two. Selecting the first arriving signal is equivalent to logical OR operation as the output rises if any of the inputs are triggered. The dual of this would imply using the AND operation for the MAX function.

### **3.1** Hardware Implementations

To see how this could ever useful, lets consider a directed acyclic graph (DAG) as shown in figure 3.3(a) which is helpful for solving many practical problems in bio-informatics, data mining, logistics, control, and information processing. Typically, a certain weight  $W_{ij}$  (figure 3.3(b)) is associated with each edge of such graph and is generally representative of a cost of satisfying certain criteria. Optimization problems then, focus on finding a path in the graph that optimizes (maximizes or minimizes) this cost function, or equivalently, navigates the shortest or longest path on such a graph.

Because DAGs can be linearized, i.e. arranged on line so that all edges go from left to right, dynamic or linear programming techniques are the most common way of solving these problems. Conceptually, dynamic programming relies on solving progressively larger sub-problems starting with the set of trivial ones, until all of them are solved, using the results of previous calculations for each new step. The topological ordering of nodes in groups (by the longest distance from root) is convenient because the score for nodes with similar distances can be calculated concurrently, since their values depend only on the scores of the lower distance

Figure 3.3: Toy DAG problem: (a) Directed acyclic graph with numbered nodes and edges. The superscript denotes the linearization index of each node while the subscript denotes the node number. (b) Equivalent scoring function that shows the edge weights  $(W_{ij}, i \text{ being the first column and j being the first row})$  connecting the nodes in tabular form.

nodes. The score for a given node calculated as a result of such recursive procedure represents the maximum or minimum distance from the root on a graph defined by weight matrix W. The actual path can be easily extracted by backtracking the graph, i.e. traversing the graph in the reverse direction and always choosing a particular edge which contributed to the score of the current node. The same procedure can be used to find optimal path for any pair of nodes, provided that such path exists.

To explain how score functions (figure 3.3(b)) are implemented with Race Logic, consider the job of one node in the graph shown in figure 3.3(a). It needs to choose the MIN of multiple different inputs, where each of those inputs is penalized by a constant value. If values are represented by a delay from a reference point t (the start of the computation), we can add a constant c to a value by simply delaying it by c time steps. More concretely a score of n, is represented by a Boolean signal 1 appearing at the output of the node n unit delays after t. As seen before, when a signal is encoded in time, the min operation on a node in the graph receiving multiple inputs is equivalent to passing along the first arriving 1, which can be implemented with a simple OR gate.

Why this works for each and every node in our DAG is by virtue of the principle of optimality which is at the heart of dynamic programming. It states that the largest problem to be solved is fundamentally identical to all its sub-problems and hence the shortest path to a given node is going to be constructed out of shortest paths of its topological predecessors. Similarly, the AND gate passes the last arriving 1, since the optimal longest path is going to consist of longest path at each previous node, causing the AND gate to perform the MAX operation. The shortest/longest path DAG problem is therefore solved by measuring the time to propagate the signal from the root node(s) to the output node(s) for a graph, in which all nodes are replaced with OR/AND gates while edges are replaced with corresponding delays. Figure 3.4 (a,b) shows an example of a particular DAG

Figure 3.4: Race formulation: (a) Longest path AND race formulation achieved by replacing edges with flip flops and nodes with AND gates. (b) Dual shortest path OR race formulation.

with two input nodes and one output node converted to AND-type and OR-type Race Logic circuits.

For synchronous Race Logic, the unit delay is assumed to be equal to one clock cycle so that D Flip Flops (DFF) gates implements delay elements. In particular, DFFs can be shift chained for the cases where the edge weight is a small number or, alternatively, an encoded configuration can be used to implement larger weights. Note that for practical reasons very large weights (or more the specifically max weight ratio) should not be too large, unless the weight is truly infinite (which can be implemented as a missing edge). The edit graph can be now thought of as a very deep pipeline, with competing paths to the final node from the root node, with all the flip flops initialized to 0. To initiate a race computation, both for the OR and AND types Race Logic, the input nodes are given a steady value of 1. With every new clock cycle, the 1 signal propagates down the edges of the graph until it reaches another node, where it gets delayed until the other inputs of the node are also 1 in the case of AND-type Race Logic, or until it just propagates through to the next edge in the case of OR-type Race Logic. For the specific DAG shown in Figure 3a, it takes two cycles for the 1 signal to propagate to the output node and it can be easily verified that this corresponds to the shortest path. Note that the shortest/longest path value can be converted back to the traditional representation with a simple counter which simply counts the number of clock cycles taken to reach the output.

Figures 3.3 and 3.4 describe the main idea for digital race logic. In these figures the weights are assumed to be fixed, so that a particular implementation finds the shortest or longest path in a fixed-weight graph. Implementing a fixed weight graph in a hardware, such as field programmable logic arrays (FPGA), just to find a shortest path may not practical. This is because implementation time overhead (e.g. configuration time in case of FPGAs) is rather substantial and will certainly overwhelm the running time of finding a shortest path between one pair of nodes. Instead, a more practical situation is to have a fixed weight graph in which some edges are controlled by some external condition, e.g. matching condition between two letters in a string (Figure 3.5). This simple modification allows for efficient reuse of the same race logic hardware, because the external conditions modify the structure of the DAG and result in different shortest path between the same nodes.

Figure 3.5: Race formulation: (a) Longest path AND race formulation achieved by replacing edges with flip flops and nodes with AND gates. (b) Dual shortest path OR race formulation.

In general, the simplest operation with race logic is to check whether the score is larger (or greater) than a certain value, i.e.  $sleaf \ge S$ . This is trivially accomplished, e.g. by checking logic after S + 1 clocks (e.g. with the help of down-counter loaded with S) if flip-flop at the output of the leaf node in question

has value of 1 propagated from the root node(s) in digital logic (Fig. 4a). By feeding every input of graph node to a circuit shown on Figure 4c the actual path corresponding to the shortest or longest path can be extracted. The idea, which works for strictly nonzero weights, is to provide an extra flip-flop per node input to trace which input(s) arrived first (or last) for OR (AND) type race logic. Initially, these flip-flops are cleared. Once the signal has propagated to one of the inputs, the particular flip-flop is toggled which disables (via EN signal) toggling of other flip-flops associated with inputs of a given node. The toggled input flip-flops can then be used to extract the actual path. Lastly, note that the number of flipflops can be greatly reduced by sharing it among different nodes output edges. For example, Figure 3.5 shows that only one flip-flop is required to implement connections from gate 2 to gates 3, 4, and 5 as compared to three in the original implementation on figure 3.4.

#### **3.2** Sequence Alignment

While the point of our work is to explore the computational potential of races, we use the well-studied problem domain of sequence alignment to test the potential of this new logic. In this section we will touch upon the extensive body of prior work on sequence alignment, talk about an important systolic array realizations and discuss other implementations ranging from supercomputing platforms to FPGA related applications. A common problem in bio-informatics is to estimate the similarity between DNA or protein sequences and there are 2 major types of motivations for DNA based sequence alignment. Currently, most whole genome projects use a shotgun sequencing strategy for genome sequencing. In a first step, genomic DNA is sheared into small random fragments. Depending on the technology, these are sequenced independently to a given length. Powerful software algorithms are then utilized to piece the resulting sequence reads back together into longer continuous stretches of sequence (contigs), a process known as de novo assembly. This is generally done when the reference sequence is unknown or there is no attempt being made to match to a reference sequence. In such applications sequence alignment forms the base alignment algorithm that is used by contig and scaffold generating software to map out the entire sequence. On the other hand, detection of issues such as aberrant methylation, in DNA sequences can that lead to cancer detection as well as a whole host of other genetic diseases, that allow a patients DNA to be mapped against a known disease to check for vulnerabilities. Alignment of 300M short reads to the Human genome takes roughly 5 hours when running on a system with dual 12-core Intel Xeon processors and 100GB of RAM. Accelerating alignment would shorten the diagnosis time, thereby allowing faster responses and increasing the number of patient samples that can be analysed per day. This would facilitate bridging the gap between research and

practice, enabling the diagnosis techniques developed to become part of routine clinical procedures.

Moving to an engineering perspective, these input patterns can have different alphabet sizes varying from 4 in the case of DNA (A, G, C, T representing the neucleo-bases) to 20 for a closely related protein comparison problem, in which strings consists of letters representing a particular amino acids [10]. A typical string similarity metric originating in information theory is the Levenshtein distance, also known as edit distance. It can be intuitively understood as the number of edit operations namely: Insertions, deletions, and substitutions, which are required to convert one string to another. To understand these edit operations let us consider string P = ACTGAGA of length N = 7 and string Q = GATTCGA of length M = 7.

Figure 3.6 shows two methods of converting P to Q. Strings that have a higher degree of similarity between each other will require less number of edit operations to convert from one to another. An alternate representation of such an operation that is very insightful is shown in figure 3.7

Figures 3.6(a), (b) show two methods of converting string P to Q. Here, columns with top row spaces represent insertions while bottom row spaces are deletions, and when lumped are known as indels. Columns with the same characters in both rows are known as matches and different ones are known as mis-

Figure 3.6: Edit operations: Multiple different ways in which simple edit operations such as insert delete and substitute can be used to convert toy DNA sequence P = ACTGAGA" to Q = GATTCGA.

matches. In particular, the first method (Fig. 1a) involves deleting letters C, G and A and inserting G, T and C, while the second method (Fig. 1c) deletes string P completely and inserts string Q. An important point to note is that even though the alignment shown in Figure 1c has no matches and is the worst case, it is still an allowed alignment. Also, the number of matches plus the number of mismatches plus the number of indels can be equal to the sum of the length of the two strings, i.e. N+M in our case, as is shown in Figure 1c, but can never exceed

Figure 3.7: Alternate alignment representations: panels (a) and (b) show two different methods of aligning the sequences P and Q from figure 3.6. Panels (c) and (d) are the respective alignment matrices.

it. Figures 3.6(c), (d) are alternate representations for two considered alignments, where the number in any position denotes the number of symbols present in figures 3.6(a), (b) up to that particular position. Note that there is only an increase in numerical value at a particular position when it houses a symbol and not a space. This representation is known as the alignment matrix as each column can be thought of as a coordinate in a two dimensional N M grid which composes the edit graph(3.8).

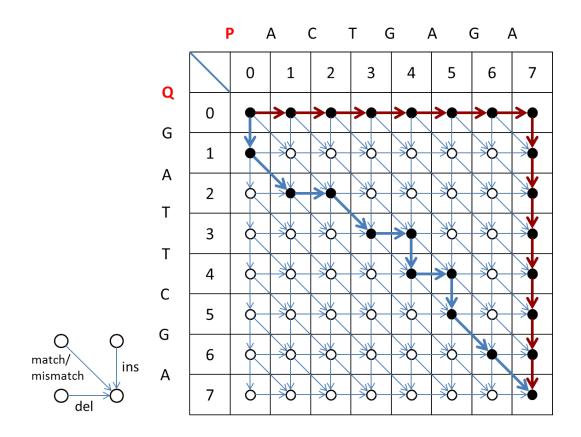

The edit graph is a directed acyclic graph (DAG) that is a two-dimensional representation of all the possible alignments between the two strings. Any particular alignment is just a path in this graph where every edge corresponds to an edit operation. The arrows show all the possible alignments; the vertical arrows representing insertions, horizontal arrows representing deletions and diagonal arrows representing matches/mismatches. For example, dark blue and dark red arrows on Figure 3.8 correspond to the two specific alignments shown on Figure 3.6(a), (b), respectively. Analyzing the merit of any particular path in the graph is equiv-

Figure 3.8: Edit Graph representation of sequence alignment. Dark red and dark blue paths are representative of the alignments shown in 3.7 (a) and (b) respectively.

alent to analyzing the merit its corresponding alignment. Given any two strings there are a large number of different paths and alignment matrices, each with its own arrangement of matches and indels. To determine the relative merit of one particular alignment over another the concept of a score matrix is introduced, which effectively defines the weight for each edge in the edit graph. Determining the goodness of the alignment is therefore finding either the longest path in the graph in the case when matches are assigned the highest values in score matrix , or, alternatively, the shortest path in the opposite case. Note that in general the penalty for the mismatch may also depend on a particular pair of letters.

| (a)                | $(s_{i-1,j} + \delta(-,P_i))$                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|

| $s_{i,j} = \max\{$ | $ \begin{cases} s_{i-1,j} + \delta(-, P_j) \\ s_{i,j-1} + \delta(Q_i, -) \\ s_{i-1,j-1} + \delta(Q_i, P_j) \end{cases} $ |

|                    | $(s_{i-1,j-1} + \delta(Q_i, P_j))$                                                                                       |

|     |   | А | С | Т | G | - |

|-----|---|---|---|---|---|---|

| (c) | А | 1 | 0 | 0 | 0 | 0 |

|     | С | 0 | 1 | 0 | 0 | 0 |

|     | Т | 0 | 0 | 1 | 0 | 0 |

|     | G | 0 | 0 | 0 | 1 | 0 |

|     | _ | 0 | 0 | 0 | 0 | 0 |

| (b)                                                                                                                                   | (d) |   | А | С | Т | G | - |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|---|---|---|---|---|---|

| $(s_{i-1,i} + \delta(-, P_i))$                                                                                                        |     | Α | 1 | 2 | 2 | 2 | 1 |

| $s_{i,j} = \min \begin{cases} s_{i-1,j} + \delta(-, P_j) \\ s_{i,j-1} + \delta(Q_i, -) \\ s_{i-1,j-1} + \delta(Q_i, P_j) \end{cases}$ |     | С | 2 | 1 | 2 | 2 | 1 |

| $\delta_{l,j} = 1 + \delta(0, P_l)$                                                                                                   |     | Т | 2 | 2 | 1 | 2 | 1 |

| $(s_{i-1,j-1} + o(q_i, r_j))$                                                                                                         |     | G | 2 | 2 | 2 | 1 | 1 |

|                                                                                                                                       |     | _ | 1 | 1 | 1 | 1 | 1 |

Figure 3.9: Score matrices: Panels (a) and (c) show score matrices that convert the edit graph problem to a longest path problem by rewarding matches with higher scores and mismatches with lower ones. The dual of this shown in panel (b) and (d).

Example max and min score functions are shown in figure 3.9(a),(b) respectively, where i and j are row and column indices as shown in 3.8. Applying equation in figure 3.9(a) and score matrix from figure 3.9(c) converts the alignment problem to a longest path problem by rewarding matches with an increase in the score by 1, while using equation in figure 3.9(b) and score matrix from figure 3.9(d) penalizes indels by 1 and mismatches by 2 and is equivalent to a shortest path problem. It is also worth mentioning that finding longest and shortest path with score matrices in figure 3.9(c),(d) are equivalent problems. The shortest path formulation is more suitable for the considered implementation is it provides a solution in a shorter time and hence is more conducive to circuit implementations.

Not only is the edit graph representation a handy tool for visualizing paths and their corresponding alignments, it is also closely tied to the concept of dynamic programming. Each node on the edit graph calculates the score corresponding to the optimal solution of the sub-problem i.e. either shortest or longest path (depending upon the score matrix) from the root node to itself. Adjacent nodes utilize these optimal solutions to calculate their own score as the computation wave proceeds along the diagonal. The edit graph itself consists of all possible alignments represented as paths from the root node to the end node and hence the above method guarantees searching of the entire space for the most optimal alignment between the given strings.

The above concepts were first brought to light in seminal works by Needleman and Wunsch [34] and Smith and Waterman [43] which in-turn spurred a considerable research interest in software and hardware methods for string comparison. Algorithms for string comparison vary from brute force dynamic programming methods to heuristic solutions that do not search the entire space but provide quick solutions [2]. The major obstacle for hardware implementations of DP sequence alignment had to do with the area complexity as the similarity metric for comparison i.e the score is cumulative and increases with array size. Any ASIC implementation would then need processing elements(PEs) that can store this worst case cumulative score and would hence lead to large, string length dependent sizes.

Lipton and Lopresti proposed a systolic array solution, that using maximum score dependent modular arithmetic, limits the number of bits of data that needs to be stored as well as shared between processing elements [24]. Hence, they were able to make sure the area scaling issues are mitigated, at the cost of extra circuitry outside of the systolic structure to recalculate the original score. To reduce the interconnect overhead, the systolic architecture utilized a tight encoding scheme that interleaves the alphabet and scores. Lipton and Lopresti not only addressed the area issue but theirs was the first paper to talk about antidiagonal independence of elements in the edit graph and utilized this property for fine grain parallelism. The resultant hardware was a linear systolic array whose processing elements could differentiate between the alphabet and scores as perform comparison and addition operations. Newer architectures [14, 15] have built upon this Lipton and Lopresti work by adding markers in processing elements to trace back optimal similarity paths. Other platforms on which sequence alignment has been performed, range from networked DEC Alpha workstations [18], to GPUs [25, 19], to Supercomputers. SIMD supercomputing platforms, such as MasParMP2 [18], that have multiple low complexity processing elements

that perform fine grain computation on multiple data streams parallely, achieving high performance at reasonable cost. On the other hand, general purpose MIMD supercomputer, Paragon [18] seemed to have performance on par with the networked DEC Alpha workstations [18]. Other implementations include FPGA based reconfigurable platforms such as Jbits [13] that utilize re-configurability to create a custom architecture using the entire string as a parameter or by defining custom instructions on FPGAs that can handle multiple input and flags at the same time to speedup computation [22]. Custom ASIC implementations such as BioSCAN utilize heuristics and a very high density implementation that results in high performance [42]. More recently, multiple freely available software tools for alignment have been developed, including Soap [23], BWA [21], and Bowtie [20]. These tools utilise the latest pattern matching algorithms and hardware technologies to perform the alignment process quickly. However, there is reliance on extensive computing resources to deliver this performance. For example, the 1000 genome project uses a 1192-processor cluster to align reads, while the BGI Bio-cloud computing platform has a current total of 14774 processors delivering 157T flops of performance though a shortcoming of such an approach is that simply scaling across more machines cannot keep up with the projected growth of sequenced data which far exceeds Moores Law.

## 3.3 Sequence Alignment as a Kernel

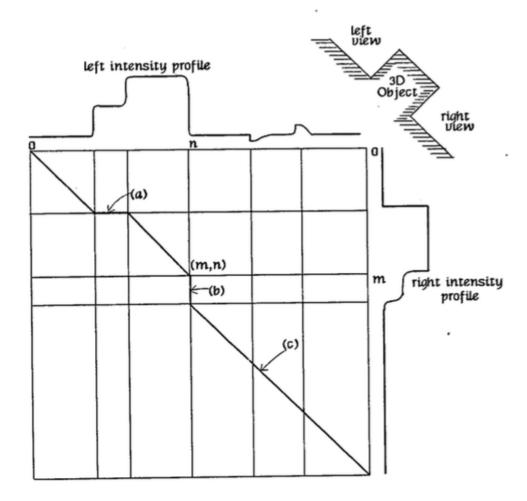

Though DNA sequence alignment is one specific application, the major concept of string, sequence, time series alignment can be found in multiple places in literature. Though the nature of the edit graph is the same in all these variations, the meaning held behind the similarity measures is different.