### University of California Santa Barbara

## Verification Techniques for Hardware Security

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy}\\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Nicole Chan Fern

### Committee in charge:

Professor Kwang-Ting (Tim) Cheng, Chair Professor Forrest Brewer Professor Tim Sherwood Dr. Çetin Kaya Koç, Lecturer Professor Huijia (Rachel) Lin

| The Diss | ertation of Nicole Chan Fern is approved |

|----------|------------------------------------------|

|          |                                          |

|          |                                          |

|          | Professor Forrest Brewer                 |

|          |                                          |

|          | D. C. M. Cl. 1                           |

|          | Professor Tim Sherwood                   |

|          |                                          |

|          | Dr. Çetin Kaya Koç, Lecturer             |

|          |                                          |

|          |                                          |

|          | Professor Huijia (Rachel) Lin            |

|          |                                          |

| · · ·    | Kwang-Ting (Tim) Cheng, Committee Ch     |

### Verification Techniques for Hardware Security

Copyright © 2016

by

Nicole Chan Fern

### Acknowledgements

I would like to acknowledge my advisor, Professor Kwang-Ting (Tim) Cheng for the support and guidance he has provided over the past 5 years. Under his mentorship I have been given the opportunity to find and define my own research question, and explore the area of hardware security. Through this process I have matured as an independent researcher and thinker, and for this I will be forever greatful.

I would also like to thank my collaborators Ismail San and Professor Çetin Koç for introducing me to the world of cryptography! Peter Lisherness has provided valuable advice about being a graduate student at UCSB in addition to facilitating an internship opportunity at Apple. My lab-mates Amirali Ghofrani, Miguel Lastras, Fan Lin, C.K. Hsu, Rui Wu, Chong Huang, Leilai Shao, and Yuyang Wang provide continuing company and support.

This work was financially supported by the National Science Foundation as well as the Semiconductor Research Corporation. I would also like to thank the Xilinx University Program for their generous donation of several FPGA boards.

Finally, I would like to thank my family and friends. Without their support, especially my husband, Jacob, and my parents, I would not have been able to complete this work.

### Curriculum Vitæ Nicole Chan Fern

#### Education

| 2016 | Ph.D. in Computer Engineering (Expected), University of California, Santa Barbara.      |

|------|-----------------------------------------------------------------------------------------|

| 2013 | M.S. in Computer Engineering, University of California, Santa Barbara.                  |

| 2011 | B.E. in Electrical Engineering, The Cooper Union for the Advancement of Science and Art |

### Work Experience

| 2013 | Hardware Verification Engineer in the Silicon Engineering Group at |

|------|--------------------------------------------------------------------|

|      | Apple Inc in Cupertino, California                                 |

| 2012 | Software Security Intern in the Cisco Security and Government      |

|      | Group at Cisco Systems in Knoxville, Tennessee                     |

#### **Publications**

- N. Fern, I. San, Ç. Koç, and K-T. Cheng. "Hardware Trojans in Incompletely Specified On-chip Bus Systems", Design, Automation, Test in Europe (DATE) Conference, 2016.

- N. Fern and K-T. Cheng. "Detecting Hardware Trojans in Unspecified Functionality Using Mutation Testing", International Conference on Computer Aided Design (ICCAD), 2015.

- N. Fern, S. Kulkarni, and K-T. Cheng. "Hardware Trojans Hidden in RTL Don't Cares Automated Insertion and Prevention Methodologies", International Test Conference (ITC), 2015.

- N. Lesperance\*, S. Kulkarni, and K-T. Cheng, "Hardware Trojan Detection Using Exhaustive Testing of k-bit Subspaces", Asia South-Pacific Design Automation Conference (ASP-DAC), 2015.

- P. Lisherness, **N. Lesperance\***, and K-T. Cheng, "Mutation Analysis with Coverage Discounting", Design, Automation Test in Europe (DATE), 2013.

- N. Lesperance\*, P. Lisherness, and K-T. Cheng, "Coverage Discounting: Improved Testbench Qualification by Combining Mutation Analysis with Functional Coverage", SRC TechCon, 2013.

- N. Lesperance\*, M. Leece, S. Matsumoto, M. Korbel, K. Lei, and Z. Dodds, "PixelLaser: Computing Range from Monocular Texture", Advances in Visual Computing, LNCS 6455, pp. 151-160, 2010.

\*Published under maiden name

#### **Activities and Academic Honors**

- Received 3rd place in the 2016 Test Technology Technical Council's E.J. McCluskey Doctoral Thesis Competition Semi-Finals

- Awarded the ECE Department Dissertation Fellowship for Spring 2016

- Teaching Assistant at UCSB for 6 academic quarters for courses requiring a weekly lecture (ECE154, Computer Architecture) and lab-based courses (ECE152A/B, students created hardware designs using a combination of FPGA boards and discrete circuit components) (2012 2015)

- Selected to teach a seminar on Matlab and also provide supplementary presentation of topics in signal processing and control systems (2010 – 2011)

- Winner of the Leon Machiz Prize for excellence in electrical engineering (2011)

- Winner of the Class of 1907 Award for the best enrolled or graduating student in calculus (2011)

- Winner of the Jesse Sherman Book Award for Outstanding Average in Electrical Engineering (2010, 2011)

- Dean's List at Cooper Union (8 consecutive semesters)

#### Abstract

### Verification Techniques for Hardware Security

by

#### Nicole Chan Fern

Verification for hardware security has become increasingly important in recent years as our infrastructure is heavily dependent on electronic systems. Traditional verification methods and metrics attempt to answer the question: does my design correctly perform the intended specified functionality? The question this dissertation addresses is: does my design perform malicious functionality in addition to the intended functionality? Malicious functionality inserted into a chip is called a *Hardware Trojan*.

This work is devoted to developing both new threat models and detection methodologies for a less studied but extremely stealthy class of Trojan: Trojans which do not rely on rare triggering conditions to stay hidden, but instead only alter the logic functions of design signals which have unspecified behavior, meaning the Trojan never violates the design specification.

The main contributions of this work are 1) precise definitions for dangerous unspecified functionality in terms of information leakage and several methods to identify such functionality, 2) satisfiability-based formal methods to test potentially dangerous unspecified functionality for the existence of Trojans, and 3) numerous examples of how the proposed Trojans can completely undermine system security if inserted in on-chip bus systems, communication controllers, and encryption IP.

# Contents

| urric | ulum Vitae                                                | $\mathbf{v}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bstra | $\operatorname{\mathbf{ct}}$                              | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| st of | Figures                                                   | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| st of | Tables                                                    | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.2   | Proposed Solution                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Har   | dware Trojans Hidden in RTL Don't Cares                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | v                                                         | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.2   |                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3   |                                                           | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4   |                                                           | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.5   |                                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | st of<br>st of<br>Intr<br>1.1<br>1.2<br>Har<br>2.1<br>2.2 | st of Figures  st of Tables  Introduction  1.1 Motivation and Problem Scope 1.2 Proposed Solution  Hardware Trojans Hidden in RTL Don't Cares 2.1 Introduction 2.1.1 Hardware Trojans 2.1.2 RTL X's and Don't Cares 2.2 Defining Malicious Don't Cares 2.2.1 Threat Model 2.2.2 Illustrative Examples 2.2.3 Formal Definition 2.3 Identification of Dangerous Don't Cares 2.3.1 Methodology 2.3.2 Existing X-Analysis Tools 2.3.3 Methodology Applied to Examples 1 and 2 2.4 Elliptic Curve Processor 2.4.1 Background 2.4.2 The Hardware Trojan 2.4.3 Automated X-Analysis |

| <b>3</b> | Ide | ntifying Dangerous Unspecified Functionality              | 34 |

|----------|-----|-----------------------------------------------------------|----|

|          | 3.1 | Introduction                                              | 34 |

|          | 3.2 | Related Work                                              | 35 |

|          | 3.3 | Information Leakage Trojans                               | 36 |

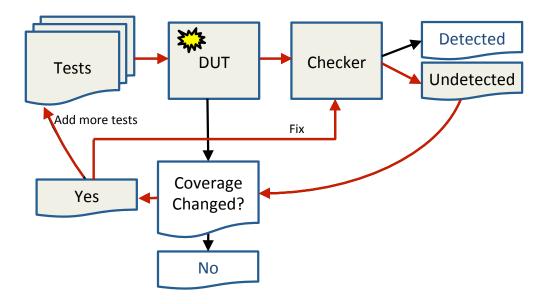

|          | 3.4 | Coverage Discounting                                      | 38 |

|          |     | 3.4.1 Motivation and Procedure                            | 38 |

|          |     | 3.4.2 Example                                             | 40 |

|          | 3.5 | Identification Methodology                                | 42 |

|          |     | 3.5.1 Threat Model                                        | 42 |

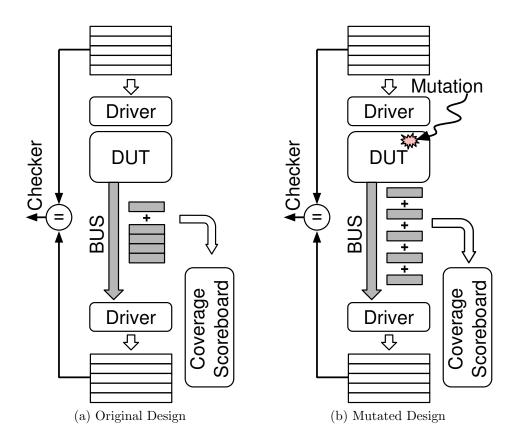

|          |     | 3.5.2 Mutant Selection                                    | 43 |

|          |     | 3.5.3 Mutant Injection and Analysis                       | 44 |

|          |     | 3.5.4 Ranking Undetected Faults                           | 47 |

|          |     | 3.5.5 Method Overhead and Coverage                        | 48 |

|          | 3.6 | UART Controller Case Study                                | 49 |

|          |     | 3.6.1 Wishbone Bus Trojan                                 | 50 |

|          |     | 3.6.2 Interrupt Output Signal                             | 54 |

|          | 3.7 | Summary                                                   | 55 |

|          |     |                                                           |    |

| 4        | Tro | jan Channels in Partially Specified SoC Bus Functionality | 56 |

|          | 4.1 | Introduction                                              | 56 |

|          | 4.2 | Related Work                                              | 58 |

|          |     | 4.2.1 Bus Security                                        | 58 |

|          |     | 4.2.2 Hardware Trojan Detection                           | 60 |

|          | 4.3 | Trojan Communication Channel                              | 61 |

|          |     | 4.3.1 Threat Model                                        | 61 |

|          |     | 4.3.2 Trojan Channel Components                           | 62 |

|          |     | 4.3.3 Topology Dependent Trojan Channel Properties        | 64 |

|          |     | 4.3.4 Protocol Dependent Trojan Channel Properties        | 65 |

|          | 4.4 | Protocol Specific Trojan Channel Definitions              | 67 |

|          |     | 4.4.1 AMBA AXI4                                           | 67 |

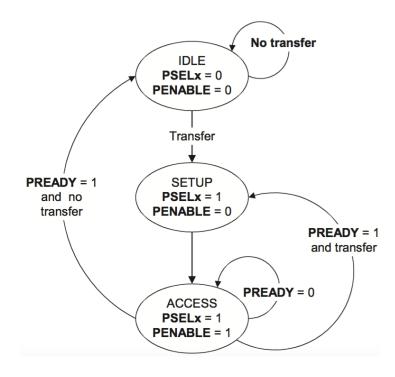

|          |     | 4.4.2 AMBA APB                                            | 69 |

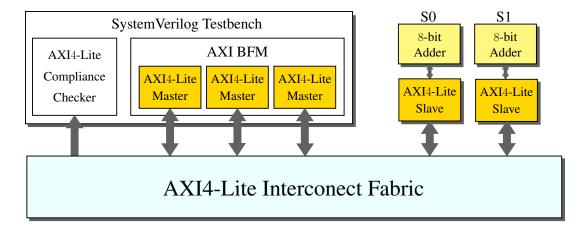

|          | 4.5 | AXI4-Lite Interconnect Trojan Example                     | 71 |

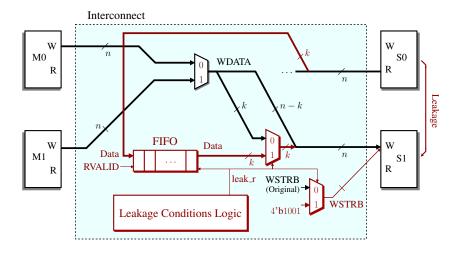

|          |     | 4.5.1 Trojan Operation                                    | 72 |

|          |     | 4.5.2 Overhead                                            | 73 |

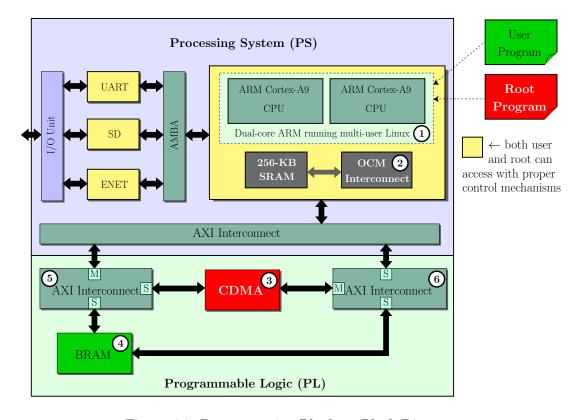

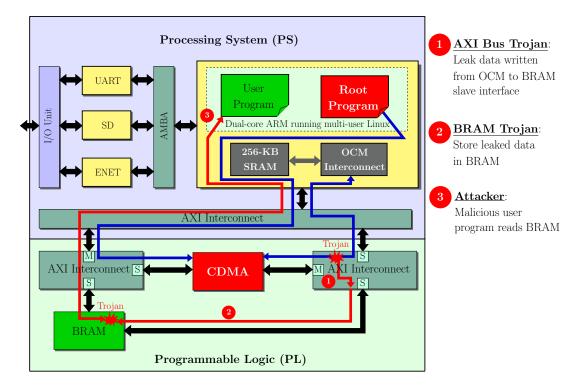

|          | 4.6 | Trojan Channel in SoC Implementation                      | 74 |

|          |     | 4.6.1 Zynq-7000 Based SoC Platform Overview               | 75 |

|          |     | 4.6.2 Hardware Trojan Operation                           | 76 |

|          | 4.7 | Details of Trojan Insertion in Xilinx IP                  | 78 |

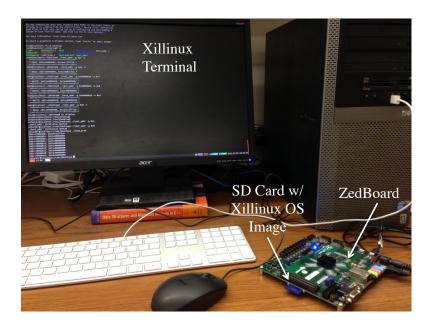

|          |     | 4.7.1 OS-Level Extraction of Trojan Channel Information   | 79 |

|          |     | 4.7.2 Overhead                                            | 80 |

|          | 4.8 | Detection Strategies                                      | 82 |

|          | 1.0 | Summary                                                   | 8/ |

| 5  | Detecting Hardware Trojans in Unspecified Functionality              | 85  |

|----|----------------------------------------------------------------------|-----|

|    | 5.1 Introduction                                                     | 85  |

|    | 5.2 Related Work: Information Flow Analysis                          | 86  |

|    | 5.3 Threat Model                                                     | 87  |

|    | 5.4 Problem Formulation                                              | 88  |

|    | 5.4.1 Identifying $(\boldsymbol{x}, \boldsymbol{\mathcal{C}})$ Pairs | 89  |

|    | 5.5 Detection Methodology                                            | 90  |

|    | 5.5.1 Overview                                                       | 90  |

|    | 5.5.2 SMT Formulas from RTL Code                                     | 91  |

|    | 5.5.3 Equivalence Checking                                           | 95  |

|    | 5.6 Case Studies                                                     | 96  |

|    | 5.6.1 Adder Coprocessor                                              | 98  |

|    | 5.6.2 UART Communication Controller                                  | 101 |

|    | 5.6.3 SMT Solving v. Equivalence Checking                            | 103 |

|    | 5.7 Summary                                                          | 105 |

| 6  | Trojan Detection Using Exhaustive Testing of k-bit Subspaces         | 106 |

|    | 6.1 Introduction                                                     | 106 |

|    | 6.2 Problem Definition and Formulation                               | 110 |

|    | 6.2.1 Interaction with Existing Test and Detection Methods           | 110 |

|    | 6.2.2 Trojan Trigger Models                                          | 110 |

|    | 6.2.3 Subspace Coverage                                              | 112 |

|    | 6.3 Our Solution                                                     | 113 |

|    | 6.3.1 Test Generation for Exhaustive $k$ -subspace Coverage          | 113 |

|    | 6.3.2 Sequential Triggers                                            | 115 |

|    | 6.3.3 Example Test Set Sizes                                         | 115 |

|    | 6.3.4 When Exhaustive $k$ -subspace Testing is Too Expensive         | 116 |

|    | 6.4 AES Trojan Case Study                                            | 119 |

|    | 6.4.1 Area Overhead                                                  | 119 |

|    | 6.4.2 Factors Influencing $k_{max}$                                  | 120 |

|    | 6.5 Summary                                                          | 121 |

| 7  | Conclusions                                                          | 122 |

| Bi | bliography                                                           | 124 |

# List of Figures

| 1.1<br>1.2 | Threats Present in the Hardware Development Lifecycle                              |

|------------|------------------------------------------------------------------------------------|

| 2.1<br>2.2 | Generic Circuit with Don't Care Bits                                               |

| 2.3<br>2.4 | Equivalence Checking Formulation Excluding Unreachable States 24 ECP State Machine |

| 3.1<br>3.2 | Coverage Discounting Flow                                                          |

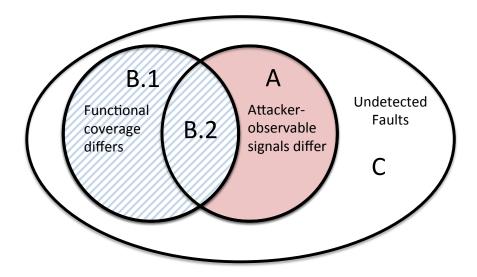

| 3.3        | Scenarios for Undetected Faults                                                    |

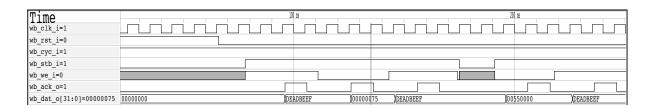

| 3.4        | Output Enable Trojan Waveform for Bus Protocol Test                                |

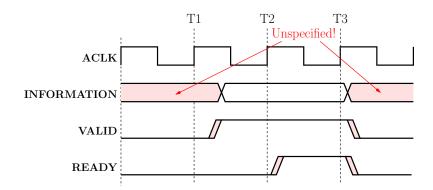

| 4.1        | AXI Bus Protocol VALID/READY Handshake                                             |

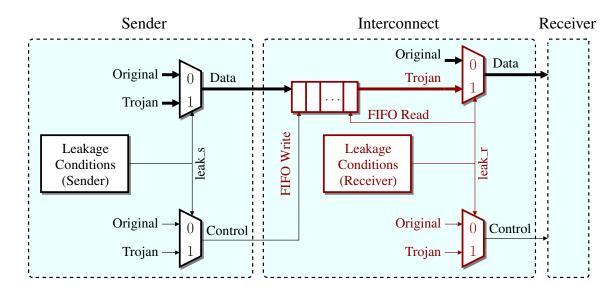

| 4.2        | Trojan Channel Circuitry                                                           |

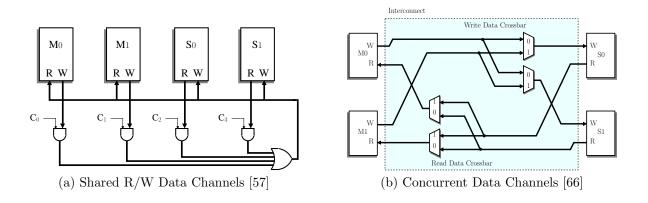

| 4.3        | Bus Topologies                                                                     |

|            | (a) Shared R/W Data Channels                                                       |

|            | (b) Concurrent Data Channels                                                       |

| 4.4        | AMBA APB Transaction State Diagram                                                 |

| 4.5        | AXI4-Lite Example System Verification Infrastructure                               |

| 4.6        | Trojan Channel Logic for AXI4-Lite Interconnect                                    |

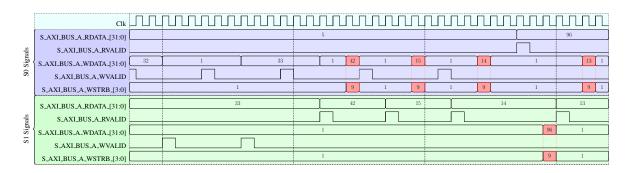

| 4.7        | 2-way Information Leakage Waveform                                                 |

| 4.8        | Demonstration Platform Block Diagram                                               |

| 4.9        | Hardware Trojan Operation                                                          |

| 4.10       | Demonstration Environment                                                          |

| 4.11       | OS-Level Trojan Demonstration Shell Commands                                       |

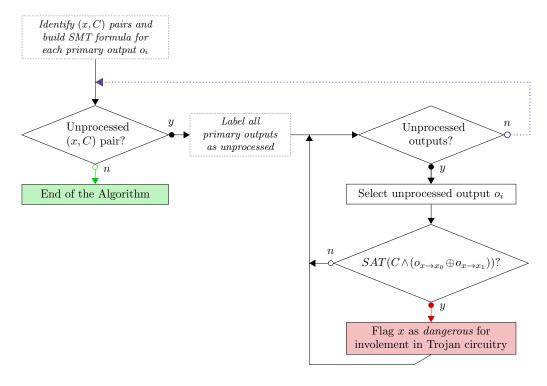

| 5.1        | Detection Methodology                                                              |

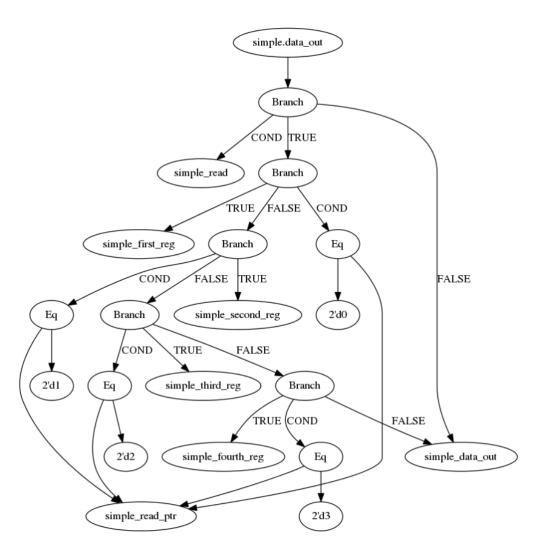

| 5.2        | Data-flow Graph for <i>simple.data_out</i> Generated by Pyverilog 92               |

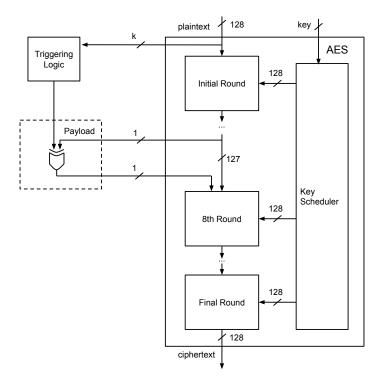

| 6.1 | AES Fault Attack Trojan                 | 108 |

|-----|-----------------------------------------|-----|

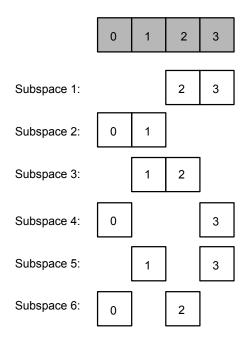

| 6.2 | All 6 2-bit Subspaces in a 4-bit Vector | 112 |

# List of Tables

| 2.1 | Classification of Don't Cares in Elliptic Curve Processor                    | 32  |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Area overhead of Specifying Don't Cares in Elliptic Curve Processor          | 33  |

| 3.1 | Categorization of Undetected Faults                                          | 50  |

| 4.1 | Trojan-Free Design Results (After Place and Route)                           | 73  |

| 4.2 | Area Overhead of 2-way HW-Trojan Channel                                     | 74  |

| 4.3 | Overhead of Programmable Logic in SoC Platform                               | 82  |

| 5.1 | Case Studies: Results Summary                                                | 97  |

| 5.2 | Trojan Detection Results for Adder Coprocessor                               | 99  |

| 5.3 | Number of Graph Nodes in Adder Coprocessor                                   | 100 |

| 5.4 | Trojan Detection Results for UART Core                                       | 102 |

| 5.5 | Number of Graph Nodes in UART Core                                           | 103 |

| 6.1 | Activation Probabilities                                                     | 111 |

| 6.2 | Test Sets for $n = 8, k = 3$                                                 | 114 |

| 6.3 | Test Set Length for Exhaustive $k$ -subspace Coverage $\ldots \ldots \ldots$ | 115 |

| 6.4 | Activation Probabilities: Strategy 2 v. Strategy 1                           | 118 |

| 6.5 | Activation Probabilities: Strategy 3 v. Strategy 1                           | 118 |

| 6.6 | Area Increase v. $k$ and $m$ (identical patterns)                            | 119 |

| 6.7 | Area Increase v. $k$ and $\#$ of Distinct Patterns                           | 120 |

## Chapter 1

## Introduction

## 1.1 Motivation and Problem Scope

Electronic devices and systems are now ubiquitous and influence key aspects of modern life such as freedom of speech, privacy, finance, science, and art. Concern about the security and reliability of our electronic systems and infrastructure is at an all-time high. Failure to protect these systems results in not only great financial hardship, but can give rise to life-threatening situations as seen when patient medical records became inaccessible within all MedStar Health hospitals after their computer networks were attacked by ransomware [1], and when cyber-attacks left nearly a quarter million people in Western Ukraine without power or heat for several hours in the dead of winter [2].

Securing electronic systems is extremely difficult because an attacker only needs to find and exploit a single weakness to perform malicious actions whereas defenders must protect the system against an infinite set of possible vulnerabilities to ensure it is secure. To address the attacker/defender asymmetry, security research has focused on developing threat models which classify attacker capabilities, motivations, and goals, and creating a taxonomy of vulnerabilities to address. For example, Ravi et al. [3] give an overview of

the threats embedded systems face and the existing catalogue of mitigation techniques.

Security techniques target detection/prevention of a class of vulnerability given a specific threat model. Identifying and disclosing (in a responsible manner) new vulnerabilities to the security community is essential to the process of making systems more secure. The task of enumerating and addressing all threat models and vulnerabilities is never complete, but this dissertation contributes to this task by discovering and developing mitigation strategies for a novel class of vulnerability: the opportunity in most hardware designs for an attacker to hide malicious behavior entirely within **unspecified** functionality.

Verification and testing is a major bottleneck in hardware design, and as design complexity increases, so does the productivity gap between design and verification [4]. It is estimated that over 70% of hardware development resources are consumed by the verification task. To address this challenge, commercial verification tools and academic research developed over the past several decades has focused on increasing confidence in the correctness of *specified functionality*. Important design behavior is modeled then various tools and methods are used to analyze the implementation at various stages in the chip design process to ensure the implementation always matches the golden reference model.

Behavior which is not modeled will not be verified by existing methods, meaning any security vulnerabilities occurring within unspecified functionality will go unnoticed. In modern complex hardware designs, which now contain several billion transistors, there always exists unspecified functionality. It is simply impossible to enumerate what the desired state of several billion transistors or logic gates should be at every cycle when behavior depends not only on the internal state of the system, but also on external input from the environment the device is embedded in. It is only feasible to model and verify aspects of the design with functional importance.

Because behaviors at a good fraction of signals for many operational cycles are unspecified, an attacker can modify this functionality with impunity without detection by existing verification methods. This thesis explores how an attacker can embed malicious behavior *completely* within unspecified functionality whereas most related research explores how to detect violations of specified behavior occurring under extremely rare conditions, where the main challenge is identifying these conditions.

Malicious functionality inserted into a chip is called a *Hardware Trojan*. Hardware Trojans are a major concern for both semiconductor design houses and the U.S. government due to the complexity of the chip design ecosystem [5, 6]. Economic factors dictate that the design, manufacturing, testing, and deployment of silicon chips is spread across many companies and countries with different and often conflicting goals and interests. If a single party involved deems it advantageous to insert a Hardware Trojan, the consequences can be catastrophic.

Goals of previously proposed Hardware Trojans range from denial of service attacks such as forcing premature circuit aging [7] and on-chip system bus deadlock [8] to subtler attacks which attempt to gain undetected privileged access on a system [9], leak secret information through power or timing side channels [10], or weaken random number generator output [11].

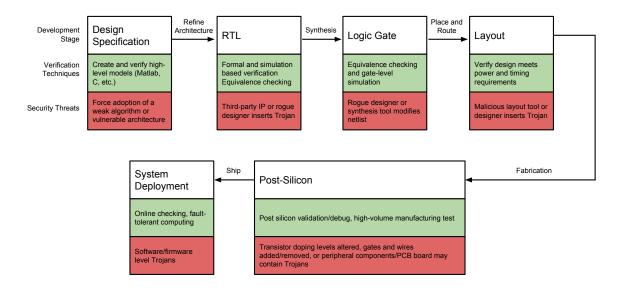

The process of transforming a document specifying how a chip should behave to physical silicon is extremely complex, involving thousands of engineers and an entire ecosystem of design tools and fabrication services. Figure 1.1 gives an overview of the design life cycle, and the Trojan threats faced at each stage. Hardware Trojans are extremely hard to defend against because they give the attacker the ability to modify the circuit at any stage in the design lifecycle to introduce new vulnerabilities, not just identify and exploit those already existing in the system [12, 13].

Before fabrication (pre-silicon), the design is modeled using an executable Register

Figure 1.1: Threats Present in the Hardware Development Lifecycle

Transfer Level (RTL) hardware description language such as Verilog or VHDL and the model is thoroughly analyzed and tested for errors. A modern design can contain several hundred Verilog/VHDL modules, some of which are provided by external (potentially untrusted) 3rd parties. Before fabrication, an RTL model must be transformed into a physical design layout, which specifies how transistors are to be arranged on the silicon wafer. This process is performed by a mix of extremely complex Electronic Design Automation (EDA) tools (which are potentially untrusted) and manual effort.

This thesis focuses on detecting Hardware Trojans inserted in the Verilog/VHDL code, which in some aspects is more challenging than the detection of Trojans inserted in the gate-level netlist, physical design layout, or during or after fabrication. The EDA ecosystem contains mature tools to ensure that once an RTL design is considered "golden", all subsequent transformations produce designs whose behavior matches that of the golden model. This work increases confidence that the RTL reference model, used as a guidepost for the rest of design development, itself is Trojan-free, which is essential to detecting

any Trojans inserted at subsequent stages in the design lifecycle.

Many of the Trojans proposed in literature hide from the verification effort using extremely rare triggering conditions. Examples of stealthy Trojan triggers are counters, which wait thousands of cycles before changing circuit functionality, or pattern recognizers, which wait for a "magic" value or sequence to appear on the system bus [14] or as plaintext input in cryptographic hardware [15, 16, 17]. Trojans with these triggering mechanisms generally deploy a payload which clearly violates system specifications (such as causing a fault during a cryptographic computation).

Existing pre-silicon Trojan detection methods assume Trojans violate the design specification under carefully crafted rare triggering conditions, and focus on identifying the structure of this triggering circuitry in the RTL code or gate-level netlist [18, 19, 20, 21]. The Trojans proposed in this dissertation do not rely on rare triggering conditions to stay hidden, but instead **only** alter the logic functions of design signals which have **unspecified behavior**, meaning the Trojan **never** violates the design specification.

Addressing this Trojan type requires a different approach from both existing Trojan detection and hardware verification methods, since traditional verification and testing excludes analysis of unspecified functionality for efficiency, and focuses primarily on conformance checking. Identifying unspecified functionality that either contains a Hardware Trojan or could be exploited by an attacker in the future is difficult because by definition unspecified functionality is not modeled or known by the design/verification team.

## 1.2 Proposed Solution

To address the threat of Trojans modifying unspecified design functionality, this thesis provides 1) precise definitions for dangerous unspecified functionality in terms of information leakage, 2) methods to test this potentially dangerous unspecified functionality for

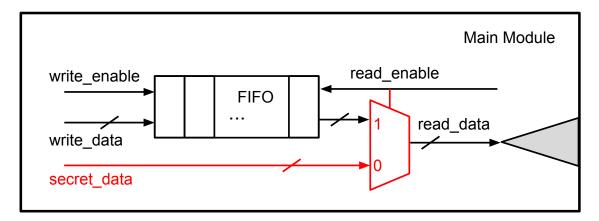

Figure 1.2: Trojan-infested FIFO (Trojan Circuitry affecting unspecified functionality to leak information shown in red)

the existence of Trojans, 3) an abstraction-level agnostic method to identify potentially dangerous unspecified functionality without requiring any prior or specialized knowledge about the design, and 4) numerous examples of how the proposed Trojans can completely undermine system security if inserted in on-chip bus systems, communication controllers, and encryption IP.

By definition, unspecified functionality should never significantly influence design behavior. One way to quantify the influence a signal, x, has in a design is to assign x different values during the conditions where x is unspecified, then check if any primary output signals or registers differ. Normally it does not matter if x propagates to other signals in the circuit when x is unspecified as long as the design functions correctly, but a key insight emphasized throughout this dissertation is that if the value of x can propagate to points the attacker can observe, it is possible for an attacker to insert a Trojan which ties x to a signal originally not accessible to an attacker. This allows an attacker to learn the value of this signal and leak important information from the circuit without violating design specifications.

For example, consider the simple first-in first-out (FIFO) buffer shown in Figure 1.2,

which writes the data currently at the input write\_data to the buffer when the signal write\_enable is 1 and the FIFO is not full, and places data from the buffer on the read\_data output when the signal read\_enable is 1 and the FIFO is not empty. What should the value of read\_data be when read\_enable is 0 or the FIFO is empty? It may seem logical to assume the value of read\_data under such conditions retains its value from the previous valid read, but what if the FIFO has never been written to or read from before? In this case the value is unknowable, and cannot be specified.

It is very likely the verification effort will only examine the value of read\_data when read\_enable is 1 and the FIFO is not empty because it is assumed that any circuitry in the fan-out of read\_data is only used during a valid FIFO read. However, this means an attacker can modify the FIFO design to leak secret information on the read\_data output during all cycles for which the unverified conditions hold. This malicious circuitry is shown in red in Figure 1.2. It should be emphasized that these conditions occur quite frequently making this Trojan behavior hard to flag using existing pre-silicon detection methodologies relying on the identification of behavior occurring only under rare conditions.

Chapter 2 focuses on a special class of unspecified functionality, RTL Don't Cares [22]. We present a novel Trojan which leaks information by modifying only existing don't care bits. RTL don't cares have long plagued chip verification due to hard-to-diagnose "X-bugs." In Chapter 2, we provide a formal automated X-analysis technique based on combinational equivalence checking which both prevents the insertion of this new Trojan type and also has the potential to uncover accidental X-bugs as well. We demonstrate our prevention methodology on an Elliptic Curve Processor design susceptible to the insertion of a Trojan capable of leaking all key bits by modifying only don't cares.

Chapter 3 presents a methodology to identify dangerous unspecified functionality beyond RTL Don't Cares [23]. Based on mutation testing, this method is capable of

identifying signals and conditions corresponding to dangerous unspecified functionality in FSM, C, SystemC, TLM, RT, and gate-level models. This chapter also provides mutant ranking heuristics to prioritize analysis of the most dangerous functionality. The presented methodology integrates easily with existing verification flows and can be run alongside Coverage Discounting [24], a technique which reflects error propagation abilities of the testbench in functional coverage metrics. This method applied to a UART controller discovered an entire class of Trojan exploiting undefined behavior in bus protocols along with poorly tested interrupt functionality.

Chapter 4 provides general guidelines for identifying dangerous unspecified functionality for an important class of design: on-chip bus systems [25]. Regardless of the specific bus topology and protocol, bus behavior is never fully specified, meaning there exist cycles/conditions where some bus signals are irrelevant, and ignored by the verification effort. Chapter 4 presents a general model for creating a covert Trojan communication channel between SoC components by altering existing on-chip bus signals only when they are unspecified and demonstrates how a Trojan channel can be inserted undetected in several widely used standard bus protocols such as AMBA AXI4 and APB. To illustrate how a Trojan channel can give an attacker a powerful foothold in a complex system, a Trojan channel is inserted in an SoC design running a multi-user Linux OS. An on-chip memory (OCM) is available to all users, but access is managed by the kernel to ensure memory isolation and privacy. The channel allows an unprivileged attacker running software on the system to access root-user memory transactions.

Chapter 5 provides an automated procedure to detect Trojan circuitry modifying unspecified design functionality. Building upon Chapters 3 and 4, which focus on identifying possibly dangerous functionality but do not classify the functionality as containing a Trojan or not, the analysis procedure in Chapter 5 takes as input unspecified functionality given as a list of  $(x, \mathcal{C})$  pairs. For a design specified as RTL code or a gate-level

netlist, a signal x, which is unspecified when a condition,  $\mathcal{C}$ , holds, our procedure determines if a Trojan is using x to leak information during  $\mathcal{C}$ . For the FIFO in Figure 1.2, the  $(x, \mathcal{C})$  pairs would be (read\_data, read\_enable == 0), and (write\_data, write\_enable == 0). The Trojan circuitry shown in red is detected by our procedure if the signal secret\_data propagates to the boundaries of the design.

For gate-level designs, the procedure formulates the Trojan detection problem in terms of combinational equivalence checking [26], a mature formal verification technique for which commercial tools with the ability to analyze industry-scale designs exist. For designs written in Verilog or VHDL, the procedure traverses the control/data-flow graph to construct formulas for the assignment of all circuit output signals and recent advances in Satisfiability Modulo Theory (SMT) solvers [27] provide the ability to determine if x can affect the formula evaluation under C, thereby indicating the presence of a Trojan. Designs analyzed include an adder coprocessor with an AXI4-Lite bus interface and a UART communication controller with a Wishbone Bus interface.

Chapter 6 details a post-silicon Trojan detection methodology developed to activate Trojans using rare conditions to trigger when malicious behavior occurs [28]. The goal of the proposed detection method is to overcome the weaknesses of existing post-silicon Trojan detection strategies which bias test vectors based on controllability and observability metrics. Our method instead uses the observation that to reduce the area/power/timing footprint of the Trojan, an attacker is likely to only use k of n controllable signals for triggering, where  $k \ll n$ , and we target exhaustive testing of all k-subspaces.

Chapter 7 summarizes our contributions and gives several possible directions for future research.

## Chapter 2

## Hardware Trojans Hidden in RTL

## Don't Cares

### 2.1 Introduction

In this chapter we present a novel Trojan which leaks information by modifying only existing don't care bits along with a formal automated X-analysis technique based on combinational equivalence checking which both prevents the insertion of this new Trojan type and also has the potential to uncover accidental X-bugs as well. We demonstrate our prevention methodology on an Elliptic Curve Processor design susceptible to the insertion of a Trojan capable of leaking all key bits by modifying only don't cares.

## 2.1.1 Hardware Trojans

Many Trojan taxonomies have been proposed [12, 29, 13], which categorize Trojans based on the design phase they are inserted, the triggering mechanism, and malicious functionality accomplished (payload). Most existing Trojans can be divided into the following categories:

- 1. The logic functions of some design signals are altered, causing the circuit to violate the system specification

- 2. The Trojan leaks information through side-channels, and no functionality of any existing signals is modified

In this chapter, we addresses a third, less studied type of Trojan:

3. The logic functions of **only** those design signals which have **unspecified behavior** are altered to add malicious functionality without violating system specifications

The key difference between Categories 2 and 3 is that Trojans in Category 3 alter the design in the boolean/functional domain, whereas Trojans in Category 2 only manipulate non-boolean side channels, and require characterization of these side channels for detection.

In this chapter, the unspecified behavior necessary to implement Trojans in Category 3 results from don't cares specified by the designer in the RTL code. We present techniques to both insert and prevent insertion of Category 3 Trojans in the RTL code or gate-level netlist. An attacker can assign values or tie other internal design signals to RTL don't cares to accomplish malicious functionality, such as leaking secret information. Prevention of this new Trojan type requires refining the system specification (Verilog code) by first identifying the "dangerous" don't cares, then disambiguating them by selecting static values to assign.

Unlike Trojans in Category 1, which often rely on rare triggering conditions to avoid causing incorrect design behavior during testing and normal design operation (ex. [14, 15, 16, 17]), our proposed Trojans are theoretically impossible to detect even if all possible input sequences are tested. Moreover, the proposed Trojans are undetectable even if a perfect sequential equivalence checker is used to check if a Trojan-infested RTL or

gate-level implementation conforms to a golden RTL design. This is because the design behavior being maliciously modified by the Trojan payload is itself unspecified in the original specification! Therefore, existing pre-silicon detection methodologies targeting identification of nearly unused circuitry, or rare node values [19, 20] do not address this new Trojan type.

IP watermarking by embedding secret information in the assignment of don't care values [30] is conceptually similar to the proposed Trojan insertion methodology, as both view RTL don't cares as an opportunity for the insertion of extra functionality.

To the best of our knowledge, [31] is the only work which recognizes the potential to implement malicious behavior in unspecified design functionality. [31] defines unspecified functionality as incompletely specified state transition and output functions, given a digital system specified as a finite-state machine (FSM). The process of logic synthesis takes an incompletely specified FSM M and transforms M to a completely specified gate-level FSM, M', which may contain additional unwanted state transitions and output assignments while still conforming to the original FSM.

The method proposed in [31] uses state reachability as a metric for trust. First the designer must manually categorize all design states as either protected or non-protected in a golden symbolic FSM model (M). If a path to a protected state exists in the gate-level implementation (M'), but does not exist in M, M' is considered untrusted.

Our work differs significantly from this approach and overcomes the following limitations of the state reachability based method for machines specified using symbolic FSM models proposed in [31]: 1) analysis must be performed on a *symbolic* representation of the design state space, 2) the labeling of protected v. non-protected symbolic states must be done manually and it is likely most designers would not have a clear idea or guidance for this labeling task, and 3) either full reachability analysis of protected states is required, making the method unscalable to modern designs, or the T flip-flops in the

circuit can be modified so no transitions from unprotected to protected states are allowed.

While it is common for protocols and controller modules to have reference state diagrams or state tables, from which a symbolic representation can be built and analyzed, often the only available specification for a complex design before logic synthesis is described in HDL such as the RTL code. We focus only on analyzing RTL don't cares since these precisely represent the freedom given to the synthesis tool for optimization and the freedom available to the attacker for implementing malicious functionality.

The second major difference between our work and [31] is that our notion of dangerous unspecified functionality is based on information leakage potential instead of protected state reachability. This has the main advantage that the designer is only required to identify attacker-observable signals, avoiding the high-effort manual categorization of symbolic states as protected or non-protected.

#### 2.1.2 RTL X's and Don't Cares

X's appearing in RTL code have different semantics for simulation and synthesis. In simulation, X's represent unknown signal values, whereas in synthesis, X's represent don't cares, meaning the synthesis tool is free to assign the signals either 0 or 1.

During simulation there are two possible sources of X's: 1) X's specified in the RTL code (either explicitly written by the designer or implicit such as a case statement with no default), and 2) X's resulting from uninitialized or un-driven signals, such as flip-flops lacking a known reset value or signals in a clock-gated block. X's from source 1 are don't cares, and are assigned values during synthesis, meaning they are *known* after synthesis, whereas X's from source 2 may be unknown until the operation of the actual silicon.

The Trojans we propose take advantage of source 1 X's, and clearly, if the design logic is fully specified, and don't cares never appear in the Verilog code, these Trojans cannot be

inserted. However, don't cares have been used for several decades to minimize logic during synthesis [32], and forbidding their use can lead to unacceptable area/performance/power overhead. For the case study presented in Section 2.4, replacing all X's in the control unit Verilog with 0's results in almost an 8% area increase for the block.

[33] and [34] give an industry perspective and overview of the many problems caused by RTL X's during chip design/verification/debug along with a survey of existing techniques and tools which address X-issues. Simulation discrepancies between RTL and gate-level versions of a design due to X-optimism and X-pessimism, and propagation of unknown values due to improper reset or power management sequences [35] are all issues addressed by existing research and commercial tools.

Our work presents yet another issue resulting from the presence of X's in RTL code, and provides further incentive to allocate verification resources to these existing X-analysis tools. However, existing tools aim to uncover *accidental* functional X-bugs, while the proposed Trojans can be considered a special pathological class of X-bug specifically crafted with malicious intent to avoid detection during functional verification.

X-analysis tools which focus only on providing RTL simulation with accurate X semantics, perform X-propagation analysis only for scenarios occurring during simulation-based verification, or formal methods which only analyze a limited number of cycles (ex. the reset sequence) do not adequately address the proposed threat. Through the examples in the remainder of the paper we aim to highlight the aspects of this new threat that differ most from the existing X-bugs targeted by commercial and academic tools.

The rest of this chapter is organized as follows: Section 2.2 states the threat model we are addressing, and presents two simple examples to illustrate how typical usage of don't cares in Verilog code can potentially lead to undesired information leakage, Section 2.3 presents an automated methodology to analyze all don't care bits in a Verilog design and classify them based on their information leakage potential, Section 2.4 shows

the application of this methodology to an Elliptic Curve Processor design with several hundred don't care bits, and Section 2.5 summarizes our contributions.

## 2.2 Defining Malicious Don't Cares

### 2.2.1 Threat Model

The Trojans we are proposing are inserted at RTL or gate-level with the aim of avoiding detection by equivalence checking against a Trojan-free RTL model. The Trojans can be inserted by a malicious CAD tool, disgruntled employee, or any person with access to the RTL code and the ability to modify either the RTL or the netlist.

Equivalence checking at the RT level of abstraction becomes conformance checking in the presence of RTL don't cares, because a single RTL specification simultaneously represents several possible valid gate-level implementations. When performing equivalence checking between an RTL and gate-level implementation, the gate-level implementation needs to match only one of all possible valid gate-level implementations specified by the RTL [26]. The proposed Trojans take advantage of this by transforming the design into a malicious, but valid implementation.

Our prevention methodology assumes the existence of a Trojan-free RTL model to perform X-analysis on, and provides an improved Trojan-free model that can be used detect any Category 3 Trojan through equivalence checking or simulation-based verification methods. Although requiring the existence of a Trojan-free RTL model may seem limiting, one should remember that before an attacker can successfully insert a Trojan by defining RTL don't cares there must exist a Trojan-free version of the RTL code containing the X's that the attacker hopes to exploit.

### 2.2.2 Illustrative Examples

Example 1: To illustrate how don't cares can be exploited to perform malicious functionality, a contrived example is presented for illustrative purposes. The module given in Listing 2.1 transforms a 4-bit input by either inverting, XORing with a secret key value, or passing the data to the output unmodified. The choice between the 3 transformations is selected using a 2-bit control signal, control. When control=11, Line 17 specifies that tmp can be assigned any value by the synthesis tool to minimize the logic used.

Listing 2.1: simple.v

```

module simple (clk, reset, control, data, key, out);

input clk, reset;

input [1:0] control;

[\mathbf{input} \ [3:0] \ data, \ key;

output reg [3:0] out;

| reg [3:0] tmp;

//tmp only assigned a meaningful value

//if\ control\ signal\ is\ 00,\ 01\ or\ 10

always @ (*) begin

case(control)

10

11

2'b00: tmp \le data;

2'b01: tmp <= data ^ key;

12

2'b10: tmp \leq \tilde{data};

13

//Trojan\ logic -----

14

15

//2 'b11: tmp <= key;

16

17

default: tmp <= 4'bxxxx;

```

```

18     endcase

19     end

20     always @ (posedge clk) begin

21     if (~reset) out <= 4'b0;

22     else out <= tmp;

23     end

24     endmodule</pre>

```

An attacker can take advantage of the implementation freedom given by the RTL by assigning key to tmp, causing the secret key value to appear at the output of this module. The Trojan can be inserted in the RTL code by uncommenting Line 15, or at gate-level by modifying the netlist after synthesis.

It should be emphasized that in either case, since the assignment of tmp during the control=11 condition is unspecified, it is impossible to detect the Trojan even if the design can be exhaustively simulated, or a perfect equivalence checker can compare the golden and Trojan implementations. Cadence Conformal LEC [36] was used to perform 2 experiments: equivalence checking between the golden and Trojan RTL, and equivalence checking between golden RTL and a Trojan-infested netlist. In both cases, the equivalence checker was unable to detect the presence of the Trojan functionality.

The don't cares assigned to tmp in Line 17 are useful to the attacker because:

- 1. The don't care assignment is reachable

- 2. A primary output (which the attacker can observe) differs depending on the value of the don't care bits

**Example 2:** In the previous example, all the don't care bits are dangerous and should be disambiguated in the RTL code. The following example, similar to Example 1 with the addition of a 3-bit FSM with 5 reachable states, illustrates that not all don't

cares are dangerous, and that the goal of any Trojan prevention or X-analysis technique is to identify only the dangerous X's and allow the synthesis tool to use the remaining don't cares for logic minimization.

Listing 2.2: simple\_state.v

```

module simple_state(clk, reset, control, data, key, out);

1

input clk, reset;

input [1:0] control;

input [3:0] data, key;

output reg [3:0] out;

reg [3:0] tmp;

reg [2:0] counter, next_counter;

|\mathbf{reg}|[3:0]| pattern;

//Truncated Counter 0-4

//5, 6, and 7 never appear

10

always @(*) begin

11

12

if (counter < 3'h4)

13

next_counter <= counter + 3'b1;</pre>

else next_counter <= 3'b0;

14

end

15

always @(posedge clk) begin

16

if ("reset) counter <= 3'b0;

17

18

else counter <= next_counter;</pre>

19

end

always @(*) begin

20

21

case (counter)

22

3'd0: pattern <= 4'b1010;

3'd1: pattern <= 4'b0101;

23

```

```

24

3'd2: pattern <= 4'b0011;

25

3'd3: pattern <= 4'b1100;

26

3'd4: pattern \leq 4'b1xx1;

27

default: pattern <= 4'bxxxx;

28

endcase

29

end

always @ (*) begin

30

31

case (control)

32

2'b00: tmp \leq data;

33

2'b01: tmp \le data \hat{key};

34

2'b10: tmp \leq \tilde{data};

35

2'b11: tmp \le data \ \hat{} \{pattern[3], pattern[2:0] \& counter\};

36

endcase

37

end

always @ (posedge clk) begin

38

39

if (\tilde{reset}) out \leq 4'b0;

40

else out <= tmp;

end

endmodule

42

```

In Listing 2.2 there are 6 total assignments of 1-bit don't care values. One could replace these X's in the Verilog code with 6 1-bit signals,  $dc_0, dc_1, ..., dc_5$ . The attacker can then choose to assign other internal design signals (such as key bits) to the don't care bits or leave them for the synthesis tool to assign. Line 27 can be re-written as:

default: pattern <=

$$\{dc_0, dc_1, dc_2, dc_3\}$$

;

Line 27 is unreachable (and thus pattern will never be assigned  $dc_0 - dc_3$ ) because the variable counter only takes on values 0-4. These X's are safe, and cannot be used to

leak information, therefore are best left in the RTL to aid in logic optimization. A more interesting X-assignment occurs on Line 26, which can be re-written as:

3'd4: pattern <=

$$\{1, dc_4, dc_5, 1\};$$

The assignment of  $\{dc_4, dc_5\}$  to pattern[2:1] is reachable, however, by manual inspection, one can see that the only assignment influenced by pattern (Line 35) contains a bitwise AND between counter and pattern[2:0], which prevents  $dc_5$  from propagating further, but not  $dc_4$ ! This is because when counter = 3'd4, Line 35 effectively becomes:

2'b11: tmp <= data

$$\{1, dc_4, 0, 0\};$$

In this example only 1 of 6 don't cares is dangerous and necessary to remove. In a design with hundreds of don't cares, it is expected that only a small subset is dangerous, which motivates why it is valuable for an X-analysis tool to take a fine-grain approach and distinguish between unreachable, reachable but non-propagating don't cares, and don't cares that have the potential to propagate to outputs or attacker observable points.

### 2.2.3 Formal Definition

The following sets of signals can be defined for any design:

S: all signals

D: don't care bits in the RTL code, where  $D \subseteq S$

$I \colon \text{signals an attacker can influence, where } I \subseteq S, \text{ and } D \subseteq I$

O: signals an attacker can observe, where  $O \subseteq S$

The following sets are defined for each  $dc_i$ ,  $dc_i \in D$ :

$O_i$ : observable signals which differ when  $dc_i = 0/1$ ,  $O_i \subseteq O$

$P_i$ : set of primary input sequences which cause signals in  $O_i$  to differ

Sets O and I can be determined based on the design specification, but it is reasonable to assume that O consists of all primary outputs and I consists of all primary inputs and don't care bits. Through the examples in the previous section, we have seen that a don't care bit,  $dc_i$ , is dangerous **iff**  $P_i \neq \emptyset$ . We will call an input sequence,  $T_i \in P_i$ , a **distinguishing input sequence** for  $dc_i$ . Our solution for identifying dangerous don't cares, given in Section 2.3, determines if  $P_i \neq \emptyset$ . For scalability reasons, our solution may over-approximate the set of don't cares classified as dangerous.

If  $dc_i$  is classified as dangerous,  $dc_i$  should be specified in the Verilog code, instead of being left as a don't care bit. If the circuit designer cannot afford to specify all dangerous don't cares due to tight area and timing constraints, the following metric based on  $|P_i|$  provides a ranking that can be used to replace the don't cares most accessible to an attacker.  $|P_i|$  reflects the information leakage potential of  $dc_i$  because if  $|P_i|$  is large, then there exist many conditions under which the attacker can learn the value of  $dc_i$ . Considering the probability of each sequence in  $P_i$  occurring during normal circuit operation, and how many sequences the attacker can force to occur can also improve the accuracy of this metric. An attacker can force a distinguishing input sequence  $T_i$ , if all signals in  $T_i$  are in I.

## 2.3 Identification of Dangerous Don't Cares

## 2.3.1 Methodology

The problem of finding if a distinguishing input sequence exists has been formulated in [37] as a sequential equivalence checking problem. In [37], the analysis was performed to find X-bugs, not prevent Hardware Trojans, but like the Trojans we are proposing, X-bugs result from reachable X-assignments that affect primary outputs in the design.

A key difference between X-bugs and the proposed Trojan type is that in many designs, for example, a serial multiplier, or the Elliptic Curve Processor analyzed in Section 2.4, the values at primary outputs during intermediate cycles in the computation typically don't matter, as long as the final computation result is correct. X's propagating to primary outputs during intermediate cycles generally aren't considered X-bugs if the final result is unaffected, however, information leakage can still occur during these intermediate cycles if the attacker can observe the primary outputs of the circuit.

The equivalence check is performed between 2 near identical versions of the design: one where  $dc_i = 0$  and one where  $dc_i = 1$ . If the designs are identical under all possible input sequences  $(P_i = \emptyset)$ ,  $dc_i$  cannot possibly be used to leak design information.

We build upon this idea further by addressing the relationship between multiple don't cares in the design, and we formulate the problem in terms of combinational equivalence checking and state reachability analysis.

While combinational equivalence checking between two nearly identical designs is efficient and scalable, state reachability analysis is not. In the Elliptic Curve Processor case study presented in Section 2.4, we illustrate how commercial code-reachability tools can be used in place of symbolic state reachability analysis to re-classify don't cares erroneously marked as dangerous after combinational equivalence checking as safe.

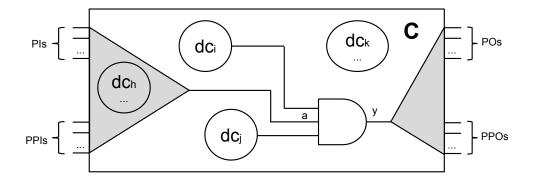

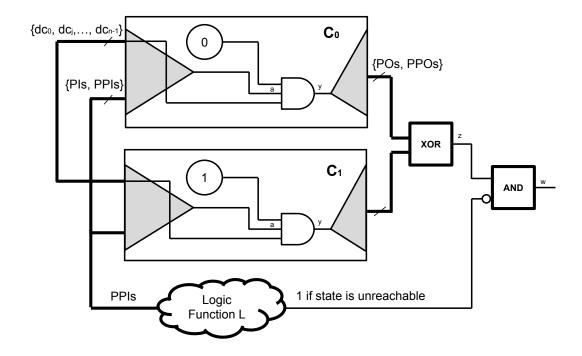

Consider the generic example circuit in Figure 2.1, where the sequential behavior has been removed by making all flip-flop inputs pseudo primary outputs (PPOs) and all flip-flop outputs pseudo primary inputs (PPIs). There are n don't care bits in the design, and it is clear that  $dc_i$  and  $dc_j$  have the ability to block each other from propagating.  $dc_h$  is in the fan-in cone for signal a, and can also influence the propagation of  $dc_i$  and  $dc_j$ , while  $dc_k$  is completely independent from  $dc_i$ ,  $dc_j$ , and  $dc_h$ .

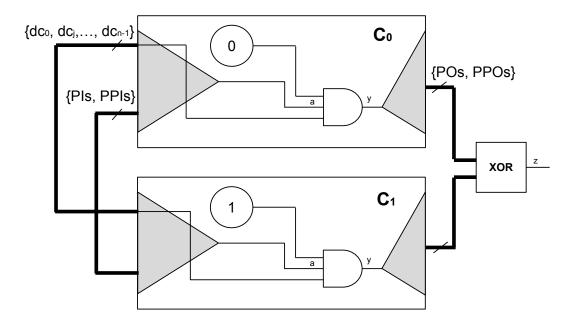

Combinational equivalence checking can be performed between 2 versions of the original design:  $C_{dc_i=0}$ , and  $C_{dc_i=1}$ , by constructing the miter in Figure 2.2 and checking the

Figure 2.1: Generic Circuit with Don't Care Bits

satisfiability of node z. If z is UNSAT, then  $dc_i$  is safe. Otherwise, the equivalence checker returns a distinguishing input vector (since we are performing combinational analysis, the distinguishing sequence is now just a single vector). Note that when analyzing  $dc_i$ , all remaining n-1 don't care bits are made primary inputs. This ensures the distinguishing input vector contains information about how the remaining don't care bits are constrained if  $dc_i$  is to successfully leak information.

Since we are not considering the sequential behavior of the design, the distinguishing input vector could require that the pseudo primary inputs be assigned a value that can never occur, in other words an unreachable state. State reachability analysis can be performed before analysis of all don't care bits, and a logic formula, L, describing the set of unreachable states can be incorporated into the miter circuit as shown in Figure 2.3 to prevent the equivalence checker from finding distinguishing input vectors containing these states.

State reachability is a hard problem, but recent advances in model checking [38] and techniques such as [39], which over-approximate the set of reachable states, can aid in addressing non-trivial designs. Additionally, since don't cares can often be traced back to single-line assignments in the Verilog code, dead-code analysis and code reachability tools can help easily eliminate don't care assignments that are unreachable.

Figure 2.2: Equivalence Checking Formulation

Figure 2.3: Equivalence Checking Formulation Excluding Unreachable States

For Trojan prevention, an over-approximation is ideal because it ensures that a dangerous don't care will never be classified as safe due to the elimination of a distinguishing input vector containing a state erroneously marked as unreachable.

Our analysis uses the robust Verilog parsing capabilities of Yosys [40] to identify don't care bits in the design, and create and write  $C_{dc_i=0}$ , and  $C_{dc_i=1}$  in the Berkeley Logic Interchange Format (BLIF). The logic synthesis tool ABC [41] is then used to perform combinational equivalence checking using the cec command. ABC is also used to compute the set of unreachable design states (which is possible for the toy examples in Section 2.2.2) using the ext\_seq\_dcs command.

#### 2.3.2 Existing X-Analysis Tools

Our experiments use ABC and Yosys because of their public availability and transparency, however we are aware that many commercial X-analysis tools and formal engines exist with the capability to perform similar analysis, such as Jasper X-prop [42], Atrenta Spyglass [43], Cadence Incisive [44], and Synopsys Magellan [45], to name only a few.

Our intention is not to argue that the existing tools are incapable of performing the necessary analysis but that settings do not exist in these tools for analyzing don't cares in a security context. We illustrate our approach in the general terms of equivalence checking and state reachability to provide a clear guide to be used by others looking to extract the same information by taking advantage of access to existing commercial tools with advance debug capabilities and optimized runtimes.

# 2.3.3 Methodology Applied to Examples 1 and 2

Our tool correctly classifies all 4 don't care bits in Example 1 as dangerous. If Example 2 is analyzed without state reachability analysis, our tool classifies all don't

cares as dangerous except for  $dc_5$ , which is classified as safe due to the bitwise AND on Line 35 which always prevents propagation. All the counterexamples for  $dc_0 - dc_3$ , assign counter to 101, which can never occur.

ABC is used to perform reachability analysis and describe the forbidden states as a logic function, L, which takes as input all pseudo-primary inputs and outputs 1 if the input combination can never occur. We then modify the miter circuit in Figure 2.2 to form the circuit in Figure 2.3 by adding an extra AND gate, with inputs L' and z. If the modified network is satisfiable, then the don't care is dangerous.

Augmenting our methodology to include state reachability information results in the correct categorization of  $dc_0 - dc_3$  as safe, leaving only  $dc_4$  classified as dangerous.

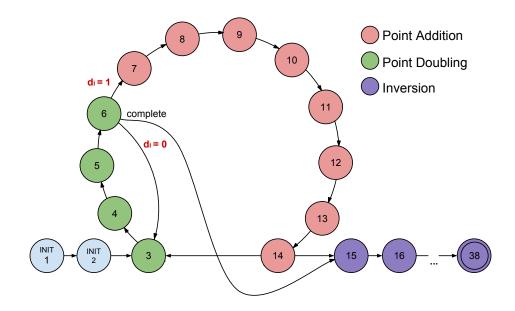

# 2.4 Elliptic Curve Processor

We now present a case study in which manual inspection was used to identify don't cares in the control unit which provide an opportunity for a Trojan to leak all key bits. We then show how our automated prevention method classifies the don't cares which make this exploit possible as dangerous in addition to unearthing several previously unknown opportunities for information leakage.

# 2.4.1 Background

Elliptic curve cryptography (ECC) is a public key cryptosystem whose fundamental operations use the mathematics of elliptic curves to perform key agreement and generate/verify digital signatures. ECC is currently used in SSH and TLS, and offers more security/key bit than RSA [46].

Like other cryptographic algorithms, ECC operations can be accelerated if implemented in hardware. Our case study examines a publicly available Elliptic Curve Pro-

cessor (ECP) which performs the point multiplication operation optimized for an FPGA implementation [47].